# DIGITAL

# **BIPOLAR**

# CMOS

# HARRIS Digital Data Book

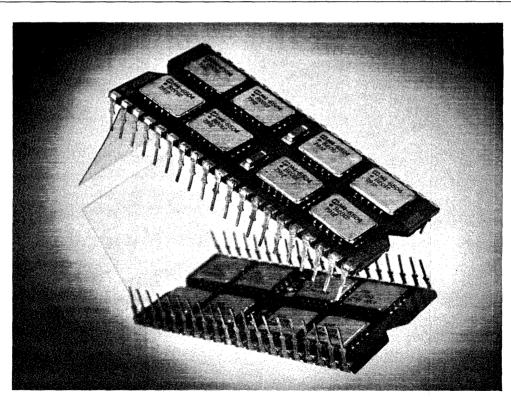

Harris Semiconductor Digital Products represent stateof-the-art in density and high speed performance. HARRIS expertise in design and processing offers the user the most reliable product available in a wide choice of formats, options, and package types. With continuing research and development and the introduction of new products, Harris will provide its customers with the most advanced technology.

This book describes Harris Semiconductor Products Division's complete line of digital products and includes a complete set of product specifications and data sheets. Also included are sections on reliability, programming, and packaging.

Please fill out the registration card at the back of this book and return it to us so we may keep you informed of our latest new product developments over the next year.

If you need more information on these and other HARRIS products, please contact the nearest HARRIS sales office listed in the back of this data book.

Harris Semiconductor's products are sold by description only. HARRIS reserves the right to make changes in circuit design, specifications and other information at any time without prior notice. Accordingly, the reader is cautioned to verify that data sheets and other information in this publication are current before placing orders. Information contained in application notes is intended soley for general guidance; use of the information for user's specific application is at user's risk. Reference to products of other manufacurers are solely for convenience of comparison and do not imply total equivalency of design, performance, or otherwise.

Copyright (C) Harris Corporation 1981

(All rights reserved)

Printed in USA

|   | i |  |  |  |

|---|---|--|--|--|

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

| : |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

|   |   |  |  |  |

| General Inform                     | ation  |

|------------------------------------|--------|

| Alpha-Numeric Index of             |        |

| Total HARRIS Product               | (1-1)  |

| Devices by Families                | (1-4)  |

| Data Sheet Classifications         | (1-5)  |

| IC Handling Procedure              | (1-6)  |

| HARRIS Memory Selection Guide      | (1-7)  |

| Bipolar PROM Cross Reference Guide | (1-8)  |

| Users' Guide to MOS Static RAMs    | (1-9)  |

| Bipolar Mei<br>CMOS Me             | •      |

| CMOS Inte                          | rface  |

| CMOS Microproce                    | essor  |

| Microprocessor Support Sys         | tems   |

| HARRIS Reliability & Qu            | uality |

iii

Ordering & Packaging

**HARRIS Sales Locations**

**Dice Information**

10

#### ANALOG DIGITAL

| HD-15531           | Manchester Encoder-Decoder                          |              | 4-60 |

|--------------------|-----------------------------------------------------|--------------|------|

| HI-200             | Dual SPST CMOS Switch                               | 3-4          |      |

| HI-201             | Quad SPST CMOS Switch                               | 3-10         |      |

| HI-300/301/302/303 | Dual SPST CMOS Switch                               | 1-18         |      |

| HI-304/305/306/307 | Dual SPST CMOS Switch                               | 1-19         |      |

| HI-381/384/387/390 | Dual SPST CMOS Switch                               | 1-20         |      |

| HI-506/507         | Single Ended 16 Channel CMOS MUX                    | 3-28         |      |

| HI-506A/507A       | Single Ended 16 Channel Overvoltage Protected       | 3-34         |      |

| HI-508/509         | Single 8 Channel CMOS MUX                           | *            |      |

| HI-508A/509A       | Single Ended 8 Channel Overvoltage Protected        | 3-40         |      |

| HI-516             | 16 Channel/Differential 8 Channel CMOS Hi-Speed MUX | 3-46         |      |

| HI-518             | 8 Channel/Differential 4 Channel CMOS Hi-Speed MUX  | 3-49         |      |

| HI-562             | 12 Bit D/A Converter                                | 4-13         |      |

| HI-1800            | Dual DPDT Switch                                    | 3-16         |      |

| HI-1818A/28A       | 8 Channel Dual 4 Channel Multiplexer                | 3-52         |      |

| HI-1840            | 16 Channel MUX-High Z                               | 3-56         |      |

| HI-5040            | SPST Switch                                         | 3-20         |      |

| HI-5040            | Dual SPST Switch                                    | 3-20         |      |

| HI-5042            | SPDT Switch                                         | 3-20         |      |

| HI-5042            | Dual SPDT Switch                                    | 3-20         |      |

| HI-5043            | DPST Switch                                         | 3-20         |      |

|                    | Dual DPST Switch                                    | 3-20<br>3-20 |      |

| HI-5045            |                                                     |              |      |

| HI-5046            | DPDT Switch                                         | 3-20         |      |

| HI-5046A           | DPDT Switch                                         | 3-20         |      |

| HI-5047            | 4PST Switch                                         | 3-20         |      |

| HI-5047A           | 4PST Switch                                         | 3-20         |      |

| HI-5048            | Dual SPST Switch                                    | 3-20         |      |

| HI-5049            | Dual DPST Switch                                    | 3-20         |      |

| HI-5050            | SPDT Switch                                         | 3-20         |      |

| HI-5051            | Dual SPDT Switch                                    | 3-20         |      |

| HI-5610            | 10 Bit Hi-Speed D/A Converter                       | 4-22         |      |

| HI-5900            | Differential DAS Front End                          | 4-35         |      |

| HI-5901            | Single Ended DAS Front End                          | *            |      |

| HM-104             | 10 x 4 50ns Diode Matrix                            |              | 2-7  |

| HM-168             | 6 x 8 50ns Diode Matrix                             |              | 2-7  |

| HM-186             | 8 x 6 50ns Diode Matrix                             |              | 2-7  |

| HM-198             | 9 x 8 50ns Diode Matrix                             |              | 2-7  |

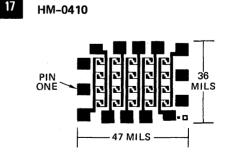

| HM-410             | 4 x 10 50ns Diode Matrix                            |              | 2-7  |

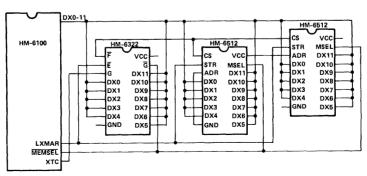

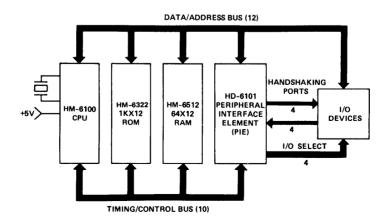

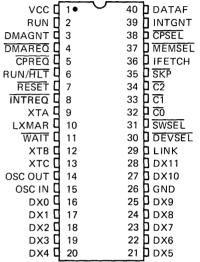

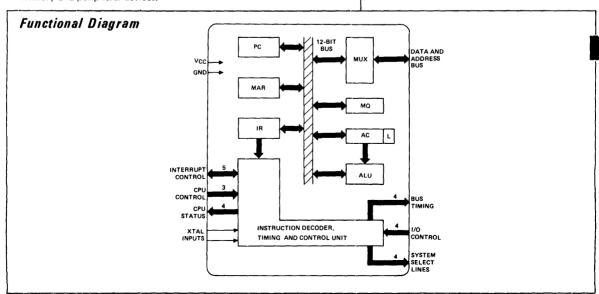

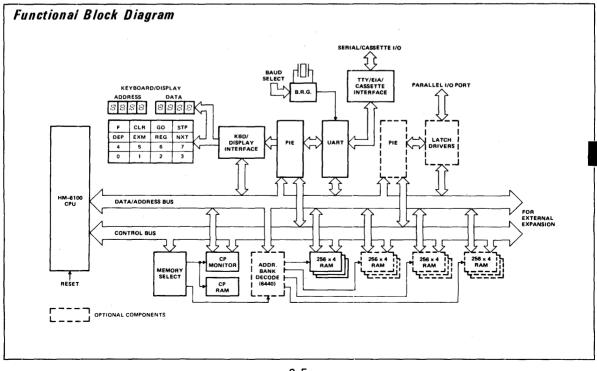

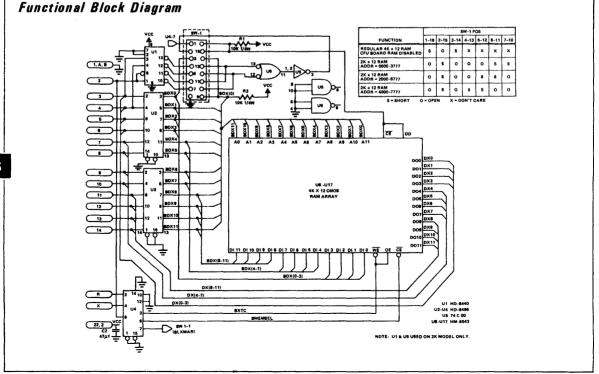

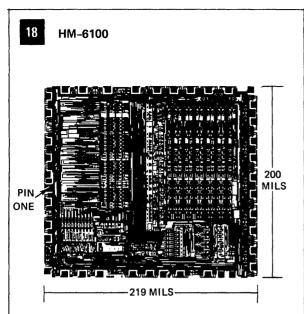

| HM-6100            | 12 Bit Static CMOS Microprocessor                   |              | 5-7  |

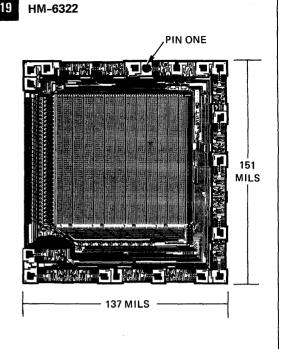

| HM-6322            | 1024 x 12 CMOS ROM                                  |              | 3-4  |

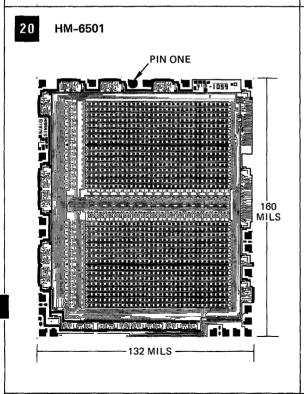

| HM-6501            | 256 x 4 CMOS RAM                                    |              | 3-10 |

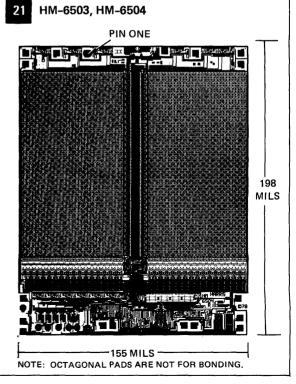

| HM-6503            | 2048 x 1 CMOS RAM                                   |              | 3-16 |

| HM-6504            | 4096 x 1 CMOS RAM                                   |              | 3-22 |

| HM-6505            | 4096 x 1 CMOS RAM                                   |              | 3-30 |

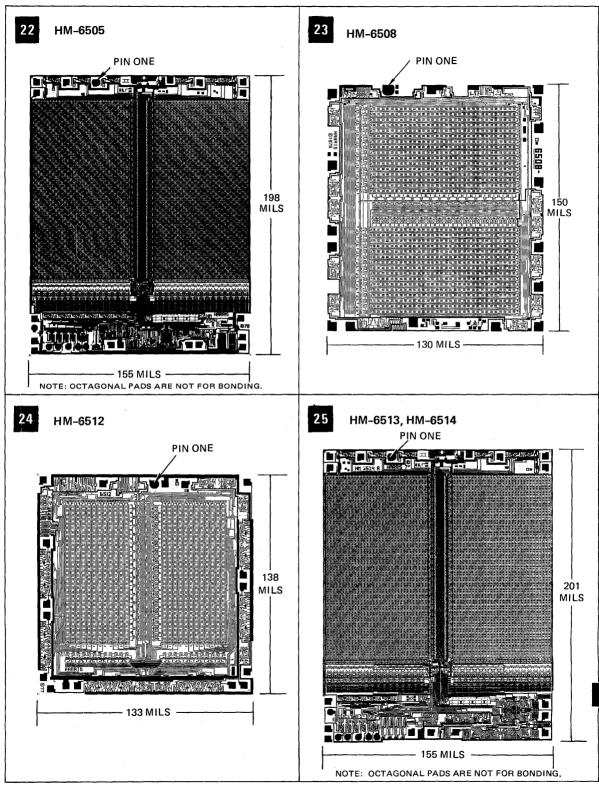

| HM-6508            | 1024 x 1 CMOS RAM                                   |              | 3-36 |

| HM-6512            | 64 x 12 CMOS RAM                                    |              | 3-42 |

| HM-6513            | 512 x 4 CMOS RAM                                    |              | 3-48 |

| HM-6514            | 1024 x 4 CMOS RAM                                   |              | 3-54 |

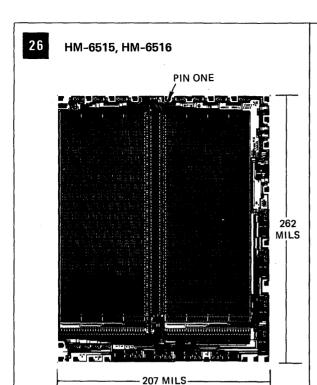

| HM-6515            | 1024 x 8 CMOS RAM                                   |              | 3-62 |

| HM-6516            | 2048 x 8 CMOS RAM                                   |              | 3-66 |

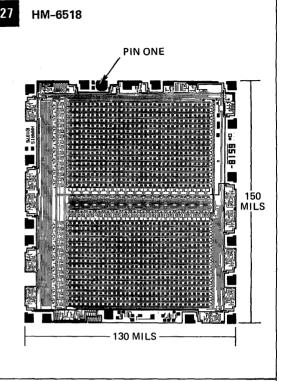

| HM-6518            | 1024 x 1 CMOS RAM                                   |              | 3-70 |

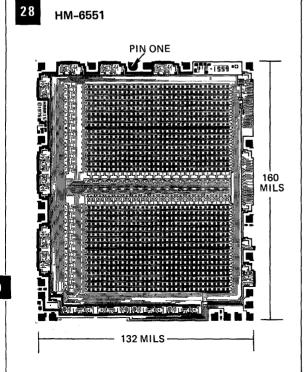

| HM-6551            | 256 x 4 CMOS RAM                                    |              | 3-76 |

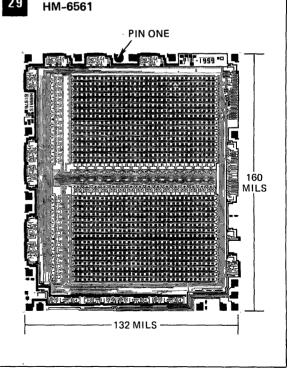

| HM-6561            | 256 x 4 CMOS RAM                                    |              | 3-82 |

|                    |                                                     |              |      |

<sup>\*</sup>Data Sheet Only

**CATALOG PAGE NUMBER**

#### **Total HARRIS Product Index**

#### **ANALOG** DIGITAL 2-6 HA-909/911 Low Noise Operational Amplifier HA-1600/02/05 Precision 10V Reference 4-2 4~6 HA-1610/15 Precision 10V Reference HA-1620/25 Precision 5V Reference 1-14 2-10 HA-2400/04/05 Programmable Analog Module HA-2420/25 Sample/Hold 4-9 HA-2500/02/05 High Slew Rate Amplifier 2-14 2-18 HA-2507/17/27 High Slew Rate Amplifier HA-2510/12/15 High Slew Rate Amplifier 2-20 HA-2520/22/25 High Slew Rate Amplifier 2-24 HA-2530/35 High Slew Rate Wideband Inverting Amplifier 2-28 2-32 HA-2600/02/05 High Impedance Amplifier 2-36 HA-2607/27 High Impedance Amplifier 2-38 HA-2620/22/25 High Impedance Wideband Amplifier HA-2630/35 2-42 Unity Volt Gain Current Amplifier High Voltage Operational Amplifier 2-46 HA-2640/45 HA-2650/55 **Dual High Performance Operational Amplifier** 2-50 HA-2700/04/05 General Purpose Amplifier 2-54 Wide Range Programmable Operational Amplifier 2-58 HA-2720/25 HA-2730/35 Wide Range Dual Programmable Operational Amplifier 2-64 HA-2900/04/05 Chopper Stabilized Operational Amplifier 2-70 HA-4602/05 2-74 High Performance Quad Operational Amplifier Wideband Quad Op Amp 2-81 HA-4622/25 HA-4741 Quad 471 Operational Amplifier 2-87 HA-4900/05 Precision Quad Comparator 2-91 2-98 HA-4920/25 High Speed Quad Comparator HA-4950 Precision High Speed Comparator 2-103 2-108 HA-5100/05 JFET Input Wideband Operational Amplifier JFET Input Wideband Operational Amplifier 2-114 HA-5110/15 1-15 HA-5130/35 Precision Operational Amplifier 1-16 HA-5160 High Slew Rate JFET Operational Amplifier HA-5190/95 Fast Settling Operational Amplifier 2-120 HC-55516/32 16kHz CVSD 5-2 1-24 HC-55536 Decode Version Only 16 Line Keyboard Encoder 5-7 HD-0165 4-3 HD-4702 Programmable Bit Rate Generator 5-29 HD-6101 Parallel Interface Element 4-7 HD-6402 Universal Asynchronous Receiver/Transmitter Asynchronous Serial Manchester Adapter (ASMA) 4-12 HD-6408 4-17 HD-6409 CMOS Manchester Encoder-Decoder (MED) 4-28 HD-6431 CMOS Hex Latching Bus Driver HD-6432 CMOS Hex Bi-directional Bus Driver 4-31 CMOS Quad Bus Separator/Driver 4-34 HD-6433 CMOS Octal Resettable Latch 4-37 HD-6434 CMOS Hex Resettable Latch 4-40 HD-6435 4-43 HD-6436 CMOS Octal Bus Buffer/Driver CMOS Latch Decoder Driver 4-46 HD-6440 HD-6495 4-50 **CMOS Hex Bus Driver** 2-4 HD-6600 Quad Power Strobe Manchester Encoder-Decoder 4-53 HD-15530

#### 1

#### CATALOG PAGE NUMBER ANALOG DIGITAL

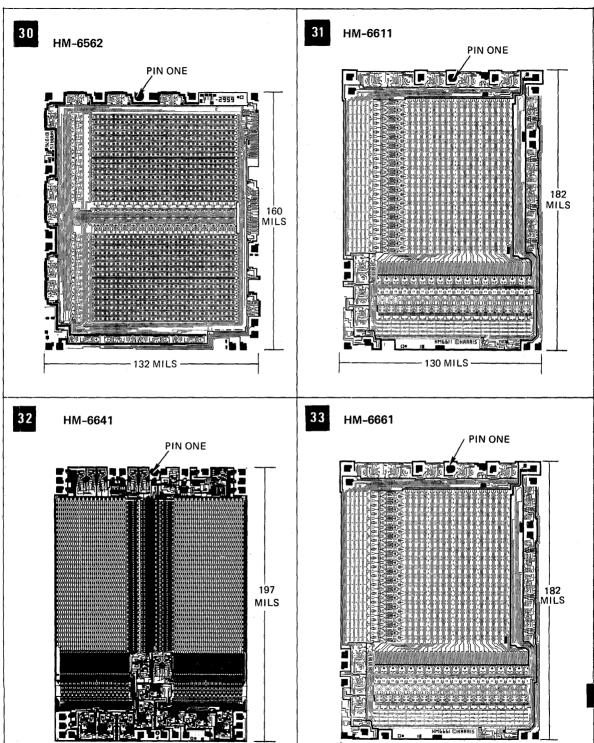

| HM-6562        | 256 x 4 CMOS RAM                                         | 3-88  |

|----------------|----------------------------------------------------------|-------|

| HM-6564        | 8192 x 8 CMOS RAM                                        | 3-94  |

| HM-6611        | 256 x 4 CMOS PROM                                        | 3-104 |

| HM-6641        | 512 x 8 CMOS PROM                                        | 3-110 |

| HM-6661        | 256 x 4 CMOS PROM                                        | 3-115 |

| HM-6716        | 2048 x 8 CMOS EPROM                                      | 3-121 |

| HM-6758        | 1024 x 8 CMOS EPROM                                      | 3-122 |

| HM-7602/03     | 32 x 8 Bit Generic PROM                                  | 2-11  |

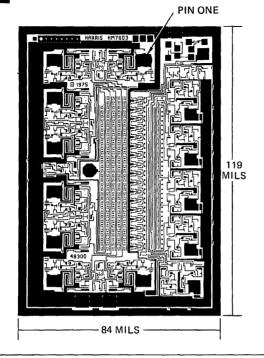

| HM-7608        | 1024 x 8 Bit Generic PROM                                | 2-50  |

| HM-7610/11     | 256 x 4 Bit Generic PROM                                 | 2-14  |

| HM-7610A/11A   | 256 x 4 Bit Generic PROM-45ns                            | 2-17  |

| HM-7620/21     | 512 x 4 Bit Generic PROM                                 | 2-20  |

| HM-7620A/21A   | 512 x 4 Bit Generic PROM-50ns                            | 2-23  |

| HM-7640/41     | 512 x 8 Bit Generic PROM                                 | 2-26  |

| HM-7640A/41A   | 512 x 8 Bit Generic PROM -50ns                           | 2-29  |

| HM-7642/43     | 1024x 4 Bit Generic PROM                                 | 2-32  |

| HM-7642A/43A   | 1024 x 4 Bit Generic PROM-50ns                           | 2-35  |

| HM-7642P/43P   | 1024 x 4 BIT Generic PROM - Power Down                   | 2-38  |

| HM-7644        | 1024 x 4 Bit Generic PROM-Active Pullup                  | 2-41  |

| HM-7647R       | 512 x 8 Bit Generic PROM-Latched Outputs                 | 2-44  |

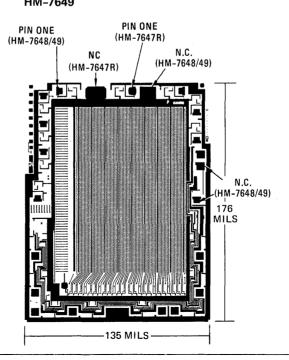

| HM-7648/49     | 512 x 8 Bit Generic PROM                                 | 2-47  |

| HM-7680/81     | 1024 x 8 Bit Generic PROM                                | 2-53  |

| HM-7680A/81A   | 1024 x 8 Bit Generic PROM-50ns                           | 2-56  |

| HM-7680R/81R   | 1024 x 8 Bit Generic PROM-Latched Outputs                | 2-59  |

| HM-7680RP/81RP | 1024 x 8 Bit Generic PROM-Powerdown with Latched Outputs | 2-65  |

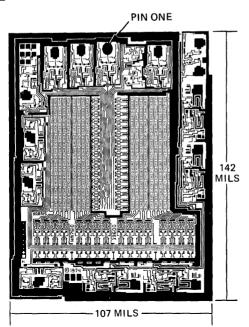

| HM-7684/85     | 2048 x 4 Bit Generic PROM                                | 2-69  |

| HM-7684P/85P   | 2048 x 4 Bit Generic PROM - Power Down                   | 2-72  |

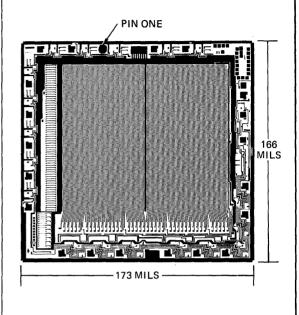

| HM-7616        | 2048 x 8 Bit Generic PROM                                | 2-75  |

| HM-76160/161   | 2048 x 8 Bit Generic PROM                                | 2-78  |

| JAN-512        | M38510/2010BJB PROM                                      | 2-81  |

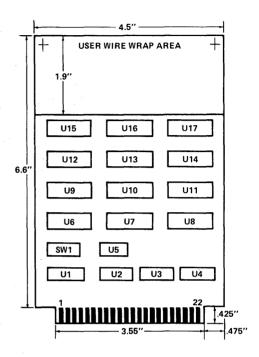

| HB-61000       | Micro-12 HM-6100 Evaluation Board                        | 6-4   |

| HB-61001       | Micro-12 4K x 12 Memory Board                            | 6-8   |

## **Devices by Families**

| Bipolar PROMs      | Page         | CMOS RAMs         | Page       |

|--------------------|--------------|-------------------|------------|

| JAN 0512           | 2-81         | HM-6501           | 3-10       |

| HM-7602/03         | 2-11         | HM-6503           | 3-16       |

| HM-7610/11         | 2-14         | HM-6504           | 3-22       |

| HM-7610A/11A       | 2-17         | HM-6505           | 3-30       |

| HM-7616            | 2-75         | HM-6508           | 3-36       |

| HM-76160/161       | 2-78         | HM-6512           | 3-42       |

| HM-7620/21         | 2-20         | HM-6513           | 3-48       |

| HM-7620A/21A       | 2-23         | HM-6514           | 3-54       |

| HM-7640/41         | 2-26         | HM-6515           | 3-62       |

| HM-7640A/41A       | 2-29         | HM-6516           | 3-66       |

| HM-7642/43         | 2-32         | HM-6518           | 3-70       |

| HM-7642A/43A       | 2-35         | HM-6551           | 3-76       |

| HM-7642P/43P       | 2-38         | HM-6561           | 3-82       |

| HM-7644            | 2-41         | HM-6562           | 3-88       |

| HM-7647R           | 2-44         | HM-6564           | 3-94       |

| HM-7648/49         | 2-47         |                   |            |

| HM-7608            | 2-50         | CMOS Interface    | Page       |

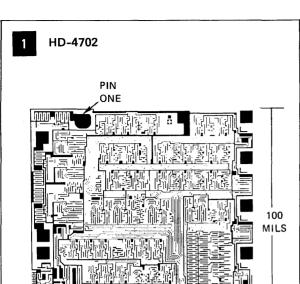

| HM-7680/81         | 2-53         | UD 4700           | 4-3        |

| HM-7680A/81A       | 2-56         | HD-4702           | 4-3<br>4-7 |

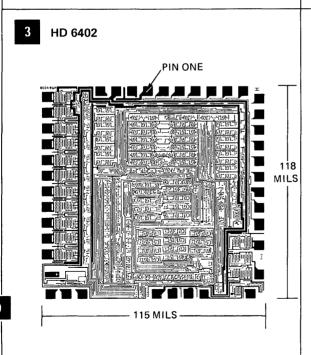

| HM-7680R/81R       | 2-59         | HD-6402           |            |

| HM-7680P/81P       | 2-62         | HD-6408           | 4-12       |

| HM-7680RP/81RP     | 2-65         | HD-6409           | 4–17       |

| HM-7684/85         | 2-69         | 01400 PD 014      | D          |

| HM-7684P/85P       | 2-72         | CMOS PROMs        | Page       |

|                    |              | HM-6611           | 3-104      |

| CMOS Bus Drivers   | Page         | HM-6641           | 3-110      |

| UD 6424            | 4-28         | HM-6661           | 3-115      |

| HD-6431<br>HD-6432 | 4-28<br>4-31 | HM-6716           | 3-121      |

| HD-6433            | 4-31         | HM-6758           | 3-122      |

| HD-6434            | 4~34<br>4-37 |                   |            |

| HD-6435            | 4-37<br>4-40 | CMOS ROMs         | Page       |

| HD-6436            | 4-43         | HM-6322           | 3-4        |

| HD-6440            | 4-45<br>4-46 | 11W-0322          | 5-4        |

| HD-6495            | 4-50         | Quad Power Strobe | Page       |

| 110 0400           | 7 00         |                   |            |

| MIL-STD-1553       |              | HD-6600           | 2-4        |

| Support Circuits   | Page         | <b>-</b>          | _          |

|                    |              | Diode Matrices    | Page       |

| HD-15530           | 4-53<br>4-60 | HM-0104           | 2-7        |

| HD-15531           | 4-60         | HM-0168           | 2-7        |

| μP                 | Dana         | HM-0186           | 2-7        |

| μΓ                 | Page         | HM-0198           | 2-7        |

| HM-6100            | 5-7          | HM-0410           | 2-7        |

| HD-6101            | 5-29         |                   |            |

#### **Data Sheet Classifications**

| CLASSIFICATION                       | PRODUCT STAGE                 | DISCLAIMERS                                                                                                                                 |

|--------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| <i>Preview</i><br>DATA<br>SHEET      | Formative or<br>Design        | This document contains the design specifications for product under development. Specifications may be changed in any manner without notice. |

| Advance<br>Information<br>DATA SHEET | Sampling or<br>Pre-Production | This is advanced information, and specifications are subject to change without notice.                                                      |

| <i>Preliminary</i><br>DATA SHEET     | First Production              | Supplementary data may be published at a later date.                                                                                        |

|                                      |                               | Harris reserves the right to make changes at any time without notice, in order to improve design and supply the best product possible.      |

#### I. C. Handling Procedures

Harris I.C. processes produce circuits more rugged than similar ones. However, no semiconductor is immune from damage resulting from the sudden application of many thousands of volts of static electricity. While the phenomenon of catastrophic failure of devices containing MOS transistors or capacitors is well known, even bipolar circuits can be damaged by static discharge, with altered electrical properties and diminished reliability. None of the common I.C. internal protection networks operate quickly enough to positively prevent damage.

It is suggested that all semiconductors be handled, tested, and installed using standard "MOS handling techniques" of proper grounding of personnel and equipment. Parts and subassemblies should not be in contact with untreated plastic bags or wrapping material. High impedance I.C. inputs wired to a P.C. connector should have a path to ground on the card.

#### HANDLING RULES

Since the introduction of integrated circuits with MOS structures and high quality junctions, a safe and effective means of handling these devices has been of primary importance. One method employed to protect gate oxide structures is to incorporate input protection diodes directly on the monolithic chip. However, there is no completely foolproof system of chip input protection in existance in the industry. In addition most compensation networks in linear circuits are located at high impedance nodes, where protection networks would disturb normal circuit operation. If static discharge occurs at sufficient magnitude (2kV or more), some damage or degradation will usually occur. It has been found that handling equipment and personnel can generate static potentials in excess of 10KV in a low humidity environment; thus it becomes necessary for additional measures to be implemented to eliminate or reduce static charge. It is evident, therefore, that proper handling procedures or rules should be adopted.

Elimination or reduction of static charge can be accomplished as follows:

- Use conductive work stations. Metallic or conductive plastic\* tops on work benches connected to ground help eliminate static build-up.

- · Ground all handling equipment.

- Ground all handling personnel with a conductive bracelet through 1-M ohm to ground.

The 1-M ohm resistor will prevent electroshock injury to personnel.

- Smocks, clothing, and especially shoes of certain insulating materials (notably nylon) should not be worn in areas where devices are handled. These materials, highly dielectric in nature, will hold, or aid, in the generation of a static change. Where they cannot be eliminated natural materials such as cotton etc. should be used to minimize charge generation capacity.

- Control relative humidity to as high as a level as practical. (RH 50%).

- Ionized air blowers reduce charge build-up in areas where grounding is not possible or desirable.

- Devices should be in conductive carriers during all phases of transport. Leads may be shorted by tubular metallic carriers, conductive foam or foil.

- In automated handling equipment, the belts, chutes, or other surfaces should be of conducting material. If this is not possible, ionized air blowers may be a good alternative.

<sup>\*</sup> Supplier 3M Company "Velostat"

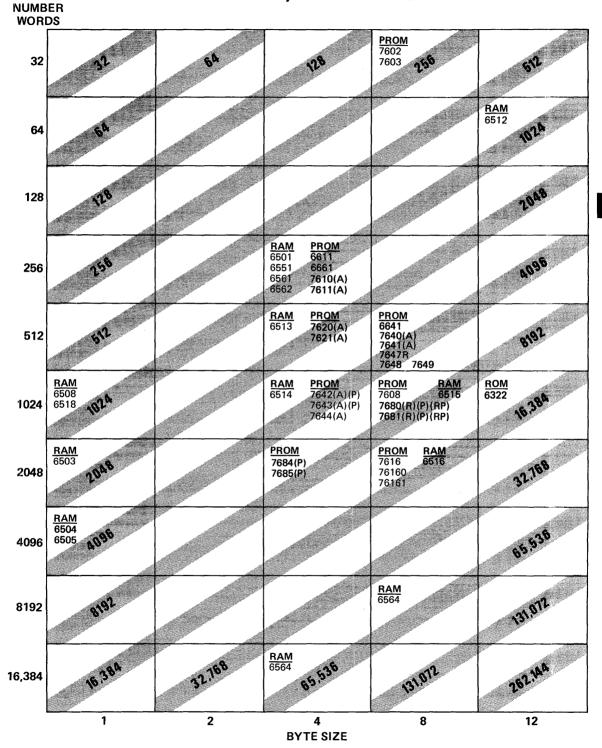

#### **HARRIS Memory Selection Guide**

1-7

# **Bipolar PROM Cross Reference**

| AMD        | HARRIS   |

|------------|----------|

| AM 27LS08  | 7602     |

| AM 27S08   |          |

| AM 29750   | ,        |

| AM 27S18   |          |

| AM 27LS09  | 7603     |

| AM 27S09   |          |

| AM 29751   |          |

| AM 27S19   |          |

| AM 27LS100 | 7610/10A |

| AM 27S10   |          |

| AM 29760   |          |

| AM 27LS20  |          |

| AM 27LS11  | 7611/11A |

| AM 27S11   |          |

| AM 29761   |          |

| AM 27LS21  |          |

| AM 27S12   | 7620/20A |

| AM 29770   |          |

| AM 27S13   | 7621/21A |

| AM 29771   |          |

| INTEL    | HARRIS   |

|----------|----------|

| 3601     | 7610/10A |

| 3621     | 7611/11A |

| 3602/02A | 7620/20A |

| 3622/22A | 7621/21A |

| 3604/04A | 7640/41A |

| 3604L    |          |

| 3624/24A | 7641/41A |

| 3605     | 7642     |

| 3625     | 7643     |

| 3608     | 7680     |

| 3628     | 7681     |

| MOTOROLA | HARRIS   |

|----------|----------|

| MCM5303A | JAN 0512 |

| MCM7640  | 7640/40A |

| MCM7641  | 7641/41A |

| MCM7642  | 7642     |

| MCM7643  | 7643     |

| MCM2708  | 7608     |

| RAYTHEON | HARRIS   |

|----------|----------|

| 29660    | 7610/10A |

| 29662    |          |

| 29661    | 7611/11A |

| 29663    |          |

| 29611    | 7620/20A |

| 29613    |          |

| 29620    | 7648     |

| 29622    |          |

| 29624    | 7640/40A |

| 29625    |          |

| 29621    | 7649     |

| 29623    |          |

| 29625    | 7641/41A |

| 29627    |          |

| 29630    | 7680     |

| 29632    |          |

| 29631    | 7681     |

| 29633    |          |

| 29634    | 7608     |

| 29635    |          |

| 29636    |          |

| 29637    |          |

| FAIRCHILD | HARRIS   |

|-----------|----------|

| 93417     | 7610/10A |

| 93427     | 7611/11A |

| 93436     | 7620/20A |

| 93446     | 7620/21A |

| 93438     | 7640/40A |

| 93448     | 7641/41A |

| 93452     | 7642     |

| 93453     | 7643     |

| 93450     | 7680     |

| 93451     | 7681     |

| INTERSIL | HARRIS   |

|----------|----------|

| 5600     | 7602     |

| 5610     | 7603     |

| 5603     | 7610/10A |

| 5623     | 7611/11A |

| 5604     | 7620/20A |

| 5624     | 7621/21A |

| 5605     | 7640/40A |

| 5625     | 7641/41A |

| 56506    | 7642     |

| 56526    | 7643     |

| NATIONAL | HARRIS   |

|----------|----------|

| DM8577   | 7602     |

| DM74S188 |          |

| DM8578   | 7603     |

| DM74S288 |          |

| DM74S3B7 | 7610/10A |

| DM74S287 | 7611/11A |

| DM74S473 | 7648     |

| DM87S295 | 7640/40A |

| DM74S472 | 7649     |

| DM87S296 | 7641/41A |

| DM74S572 | 7642     |

| DM74S573 | 7643     |

| DM87S229 | 7680     |

| DM87S228 | 7681     |

| DM74S672 | 7684     |

| DM74S673 | 7685     |

| DM27LS08 | 7608     |

| SIGNETICS | HARRIS   |

|-----------|----------|

| 82523     | 7602     |

| 82S123    | 7603     |

| 82S27     | 7610/10A |

| 82S126    |          |

| 82S129    | 7611/11A |

| 82S130    | 7620/20A |

| 82\$131   | 7621/21A |

| 825146    | 7648     |

| 82\$140   | 7640/40A |

| 82S147    | 7649     |

| 82S141    | 7641/41A |

| 82S136    | 7642     |

| 82S137    | 7643     |

| 82\$180   | 7680     |

| 82\$181   | 7681     |

| 8252708   | 7608     |

| 82\$184   | 7684     |

| 82\$185   | 7685     |

| 825190    | 76160    |

| 825191    | 76161    |

| FUJITSU | HARRIS   |

|---------|----------|

| MB7056  | 7602     |

| MB7051  | 7603     |

| MB7057  | 7610/10A |

| MB7052  | 7611/11A |

| MB7058  | 7620/20A |

| MB7053  | 7620/21A |

| MB7059  | 7642     |

| MB7054  | 7643     |

| MB7060  | 7680     |

| MB7055  | 7681     |

| NMI   | HARRIS   |

|-------|----------|

| 6330  | 7602     |

| 6331  | 7603     |

| 6300  | 7610/10A |

| 6301  | 7611/11A |

| 6305  | 7620/20A |

| 6306  | 7621/21A |

| 6348  | 7648     |

| 6340  | 7640/40A |

| 6349  | 7649     |

| 6341  | 7641/41A |

| 6352  | 7642     |

| 6353  | 7643     |

| 6380  | 7680     |

| 6381  | 7681     |

| 6385  | 7608     |

| 63100 | 7684     |

| 63101 | 7685     |

| NEC    | HARRIS   |

|--------|----------|

| μPB403 | 7610/10A |

| μPB405 | 7640/40A |

| μPB425 | 7641/41A |

| µPB406 | 7642     |

| µPB426 | 7643     |

| µPB408 | 7680     |

| μPB428 | 7681     |

| µPB427 | 7608     |

| TEXAS INST. | HARRIS   |

|-------------|----------|

| 74S188/188A | 7602     |

| 74\$288     | 7603     |

| 74186       | JAN 0512 |

| 74S387      | 7610/10A |

| 74\$287     | 7611/11A |

| 748473      | 7648     |

| 748475      | 7640/40A |

| 748472      | 7649     |

| 748474      | 7641/41A |

| 748477      | 7642     |

| 745476      | 7643     |

### <del>1</del>-9

#### Users' Guide to MOS Static RAMs

|                             |                                                  |          | RIS          |                      |              |                                                  | 2                                                |      |              | Ī              |              | SIL          | MICRO POWER<br>SYSTEMS |                                                  | BISHI      | ×            | ROLA         | NAL                                              |              |                                                  |                      | TICS         | SOLID STATE<br>SCIENTIFIC                        | ITEK         |                      | A B                                              |              |

|-----------------------------|--------------------------------------------------|----------|--------------|----------------------|--------------|--------------------------------------------------|--------------------------------------------------|------|--------------|----------------|--------------|--------------|------------------------|--------------------------------------------------|------------|--------------|--------------|--------------------------------------------------|--------------|--------------------------------------------------|----------------------|--------------|--------------------------------------------------|--------------|----------------------|--------------------------------------------------|--------------|

| SIZE &<br>ORGAN-<br>IZATION | TYPE                                             | PINS     | HARRIS       | AMD                  | IMA          | EA                                               | FUJITSU                                          | 5    | GTE          | нтасні         | INTEL        | INTERSIL     | MICRO                  | MITEL                                            | MITSUBISHI | MOSTEK       | MOTOROLA     | NATIONAL                                         | N<br>EC      | OK!                                              | RCA<br>A             | SIGNETICS    | SOLID                                            | SYNERTEK     | F                    | TOSHIBA                                          | SILOG        |

| 64 x 12                     | CMOS                                             | 18       | 6512         |                      |              |                                                  |                                                  |      |              |                | F            | 6512         |                        |                                                  |            |              |              |                                                  |              |                                                  |                      |              |                                                  |              |                      |                                                  |              |

| 411                         | 21100                                            | 16       | 6508         |                      | 6508         |                                                  | 8401                                             |      |              |                |              | 6508         | 6508                   | 1902                                             |            |              | 7001<br>6508 | 6508<br>74C929                                   | 443          |                                                  | 6508<br>5001<br>1821 |              | 5102                                             | 5102         | 6508                 | 5508                                             |              |

| 1K                          | CMOS                                             | 18       | 6518         | <b>-</b>             | 6518         | <del>                                     </del> | <b></b>                                          | _    |              |                |              | 6518         | 6518                   |                                                  |            |              | 6518         | 6518                                             |              |                                                  |                      |              | <del>                                     </del> |              | <b></b>              |                                                  |              |

| 1K x 1                      | NMOS                                             | 16       |              | 9102                 | 4015<br>4025 |                                                  | -                                                |      |              |                | 2102<br>2125 |              |                        | <del>                                     </del> |            | 4102         | 2125<br>2115 | 74C930<br>2102                                   | 2102<br>2125 | _                                                |                      | 2102<br>2125 | <del> </del>                                     | 2102         | 2102<br>4033         | -                                                | -            |

|                             | <del>                                     </del> | 16       | 6562         | <u> </u>             | 1020         |                                                  | <del>                                     </del> |      |              |                | 2.20         | <b></b>      |                        |                                                  | ·          |              |              | <del>                                     </del> |              | <del>                                     </del> |                      |              | -                                                |              |                      | <del>                                     </del> |              |

|                             |                                                  | 18       | 6561         |                      |              |                                                  | <b>†</b>                                         |      |              |                |              | 6561         |                        | 1                                                |            |              |              | 74C921                                           |              |                                                  |                      |              |                                                  |              |                      |                                                  |              |

| 1K                          | CMOS .                                           | 22       | 6501         | <b></b>              | 5101         |                                                  |                                                  |      |              | 435101         | 5101         |              |                        |                                                  |            |              | 145101       | 6552                                             | 5101<br>510L |                                                  | 5040<br>5101         |              |                                                  | 5101         | 5101                 | 5007<br>5501                                     | -            |

|                             |                                                  | 22<br>22 | 6551         |                      |              |                                                  |                                                  |      |              |                |              | 6551         |                        |                                                  |            |              |              | T4C920<br>6551                                   | 3102         |                                                  | 1822                 |              |                                                  |              |                      | .5101                                            |              |

|                             |                                                  | 16       |              | 9112                 |              | 2112                                             |                                                  |      |              |                | 2112         |              |                        |                                                  |            |              |              | 2112                                             |              |                                                  | 4112                 | 2112<br>2606 |                                                  | 2112         | 4043                 |                                                  | <u> </u>     |

| 256 x 4                     | NMOS                                             | 18       |              | 2112<br>9111         |              | 2111                                             |                                                  |      |              |                | 2111         |              |                        |                                                  |            |              |              | 2111                                             | 2111         |                                                  | 4111                 | 2111         |                                                  | 2111<br>2112 | 4042                 |                                                  |              |

|                             |                                                  | 22       |              | 2101<br>9101         |              | 2101                                             |                                                  | 4256 |              |                | 2101         |              |                        |                                                  |            |              |              | 2101                                             | 2101         | ì                                                | 4101                 | 2101         |                                                  | 2101         | 4039                 |                                                  |              |

| 2K                          | CMOS                                             | 18       | 6503         |                      |              |                                                  |                                                  |      |              |                |              |              |                        |                                                  |            |              |              |                                                  |              |                                                  |                      |              |                                                  |              |                      |                                                  |              |

| 2K x 1                      | NMOS                                             | 18       |              |                      |              |                                                  |                                                  |      |              |                |              |              |                        |                                                  |            |              |              |                                                  |              |                                                  |                      |              |                                                  |              |                      |                                                  |              |

| 2K                          | CMOS                                             | 18       | 6513         |                      |              |                                                  |                                                  |      |              |                |              |              |                        |                                                  |            |              | <u> </u>     |                                                  |              | Ĺ                                                |                      | L            |                                                  |              |                      |                                                  | <u> </u>     |

| 512 x 4                     | NMOS                                             | 18       |              |                      |              |                                                  |                                                  |      |              |                | 2113         |              |                        |                                                  |            | <u> </u>     |              |                                                  |              |                                                  |                      | ļ            |                                                  |              |                      |                                                  | <u> </u>     |

| 4K                          | смоѕ                                             | 18       | 6504<br>6505 |                      |              |                                                  | 8404                                             |      |              | 4315<br>6147   |              | 6504<br>6505 | 6504                   |                                                  |            |              | 6504         | 6504<br>6847                                     |              | 5104                                             |                      |              |                                                  |              |                      | 5504                                             |              |

| 4K x 1                      | NMOS                                             | 18       |              | 9145<br>9147         | 4017<br>2147 |                                                  | 2147                                             |      | 4104<br>4200 | 6147<br>4847   | 2141<br>2147 | 2147         |                        |                                                  |            | 4104<br>2147 | 2147         | 2141<br>2147                                     | 4104<br>2147 |                                                  |                      | 2613         |                                                  | 2147         | 2147<br>4044<br>4045 | 315D                                             | 4104<br>6104 |

|                             |                                                  | 22       |              | 9140                 |              |                                                  |                                                  | 4200 |              |                |              |              |                        |                                                  |            |              |              |                                                  |              |                                                  |                      |              |                                                  |              |                      |                                                  |              |

| 4K                          | CMOS                                             | 18       | 6514         |                      |              |                                                  | 8414                                             |      |              | 6148<br>4334   |              | 6514         | 6514                   | 21C14                                            | 58981      |              | 6514         | 6514<br>6848                                     | 444          | 5114<br>5115                                     | 5114                 |              |                                                  |              |                      | 5514                                             |              |

|                             |                                                  | 20       |              |                      |              |                                                  |                                                  |      |              |                |              |              |                        |                                                  |            |              |              |                                                  | 445          |                                                  | <u> </u>             | -            |                                                  | 2114         |                      | 5047                                             | <b></b>      |

| 1K x 4                      | NMOS                                             | 18       |              | 9124<br>9135<br>9114 | 2114         |                                                  |                                                  |      | 2114<br>4804 | 472114<br>6148 | 2114<br>2148 | 2148         |                        |                                                  |            | 2148         | 2114<br>2148 | 2148<br>2114                                     | 2114         | 2114                                             |                      | 2614         |                                                  | 2114         | 2114<br>4045<br>4047 | 314A                                             |              |

| III X 4                     |                                                  | 20       |              | 9148                 |              |                                                  |                                                  |      |              |                | 2142         |              |                        |                                                  |            |              |              | 2141<br>2142                                     |              |                                                  |                      |              |                                                  | 2142         |                      |                                                  |              |

|                             |                                                  | 22       |              | 9130<br>9131         |              |                                                  |                                                  |      |              |                |              |              |                        |                                                  |            |              |              |                                                  |              |                                                  |                      |              |                                                  |              |                      |                                                  |              |

| 8K                          | CMOS                                             | 24       | 6515         |                      |              |                                                  |                                                  |      |              |                |              |              |                        |                                                  |            |              |              |                                                  |              |                                                  |                      |              |                                                  |              |                      |                                                  |              |

| 1K x 8                      | NMOS                                             | 24       |              |                      |              |                                                  |                                                  |      | 8118         |                |              |              |                        |                                                  |            | 4118<br>4801 |              |                                                  | µPD<br>421-3 |                                                  |                      |              |                                                  |              |                      |                                                  |              |

| 16K                         | CMOS                                             | 24       | 6516         |                      |              |                                                  |                                                  |      |              | 6116           |              |              |                        |                                                  |            |              |              |                                                  | μPD<br>446   |                                                  |                      |              |                                                  |              |                      | 5516                                             |              |

| 2K x 8                      | NMOS                                             | 24       |              |                      |              |                                                  |                                                  |      |              |                |              |              |                        |                                                  |            | 4802         |              |                                                  |              | 2128                                             |                      |              |                                                  |              | 4016                 | 2016                                             |              |

#### **Product Index**

|                        |                                  | PAGE |

|------------------------|----------------------------------|------|

| HD-6600                | Quad Power Strobe                | 2-4  |

| HM-0168                | 6 x 8 Monolithic Diode Matrices  | 2-7  |

| HM-0186                | 8 x 6 Monolithic Diode Matrices  | 2-7  |

| HM-0410                | 4 x 10 Monolithic Diode Matrices | 2-7  |

| HM-0104                | 10 x 4 Monolithic Diode Matrices | 2-7  |

| HM-0198                | 9 x 8 Monolithic Diode Matrices  | 2-7  |

| HM-7602/03             | 32 x 8 PROM                      | 2-11 |

| HM-7610/11             | 256 x 4 PROM                     | 2-14 |

| HM-7610A/11A           | 256 x 4 PROM                     | 2-17 |

| HM-7620/21             | 512 x 4 PROM                     | 2-20 |

| HM-7620A/21A           | 512 x 4 PROM                     | 2-23 |

| HM-7640/41             | 512 x 8 PROM                     | 2-26 |

| HM-7640A/41A           | 512 x 8 PROM                     | 2-29 |

| HM-7642/43             | 1K x 4 PROM                      | 2-32 |

| HM-7642A/43A           | 1K x 4 PROM                      | 2-35 |

| HM-7642P/43P           | 1K x 4 PROM                      | 2-38 |

| HM-7644                | 1K x 4 PROM                      | 2-41 |

| HM-7647R               | 512 x 8 PROM                     | 2-44 |

| HM-7648/49             | 512 x 8 PROM                     | 2-47 |

| HM-7608                | 1K x 8 PROM                      | 2-50 |

| HM-7680/81             | 1K x 8 PROM                      | 2-53 |

| HM-7680A/81A           | 1K x 8 PROM                      | 2-56 |

| HM-7680R/81R           | 1K x 8 PROM                      | 2-59 |

| HM-7680P/81P           | 1K × 8 PROM                      | 2-62 |

| HM-7680RP/81RP         | 1K x 8 PROM                      | 2-65 |

| HM-7684/85             | 2K x 4 PROM                      | 2-69 |

| HM-7684P/85P           | 2K x 4 PROM                      | 2-72 |

| HM-7616                | 2K x 8 PROM                      | 2-75 |

| HM-76160/161           | 2K x 8 PROM                      | 2-78 |

| JAN-0512               | 512 Bit PROM                     | 2-81 |

|                        | MIL/M38510/20101                 |      |

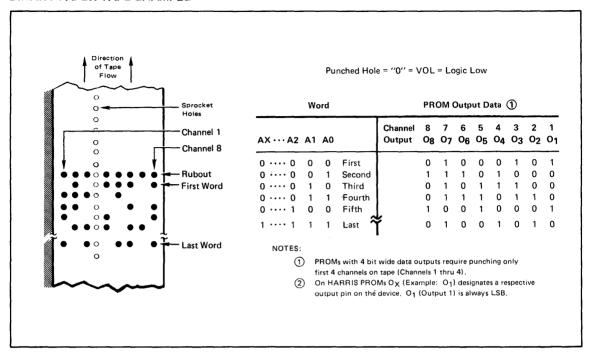

| PROM Programming       |                                  | 2-86 |

| Programmer Evaluation  |                                  | 2-89 |

| Data Entry Formats for | HARRIS Custom Programming        | 2_90 |

#### **ABSOLUTE MAXIMUM RATINGS**

As with all semiconductors, stresses listed under "Absolute Maximum Ratings" may be applied to devices (one at a time) without resulting in permanent damage. This is a stress rating only. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. The conditions listed under "Electrical Characteristics" are the only conditions recommended for satisfactory operation.

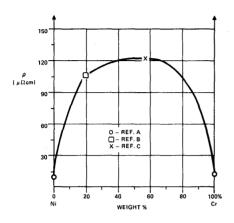

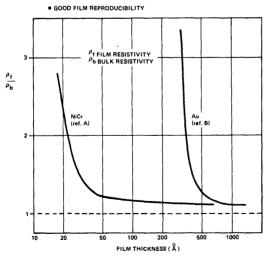

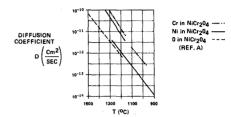

# Harris Generic Programmable Read Only Memories

In 1970, Harris offered the industry's first Bipolar programmable read only memory, and has been a leader in the field of Bipolar PROMs from 1970 to date. Harris PROMs are manufactured using the Bipolar Junction Isolation process with reliability provennickel-chromium fusible links. Harris has had experience with nickel chromium since 1964 when it was first used for high reliability military circuits because of its high stability characteristics. Harris has been manufacturing nickel-chromium fuse links since 1970 when the first PROM was manufactured, and has become the industry's most extensive programmable read only memory concept. This history has been a factor in giving Harris PROMs the industry's high programming yield and a proven level of quality and reliability.

We now employ a shallow diffused self-aligned emitter aperture process combined with two-level aluminum interconnect. This state of the art process technology has been deployed to produce large format devices with the high speed and versatility required by the industry.

Today Harris offers a family of programmable read only memories which we call the Generic PROMs or GPROMs. They have the following characteristics:

- Coherent part numbering scheme, the 76xxx series.

- Identical programming procedure for all GPROMs.

- All parameters are guaranteed over full temperature and voltage.

- The GPROM family comprises a complete range of formats.

#### JAN QUALIFIED PROMS

The Harris Semiconductor Bipolar manufacturing line has received certification for processing JAN product. There are five QPL I qualified PROMs. Five additional HARRIS PROMs have been granted QPL II listing pending QPL I approval and may be shipped as JAN qualified product. Additional HARRIS PROMs are at various stages of qualification and the status of each at press time is listed below. As the status of these products will change rapidly, we suggest that you contact the nearest Harris Representative or Harris Sales Office for current status.

| HARRIS PART# | SLASH SHEET           | STATUS |

|--------------|-----------------------|--------|

| JAN 0512     | MIL-M-38510/20101 BJB | QPL I  |

| HM1-7610     | MIL-M-38510/20301 BEB | QPL I  |

| HM1-7611     | MIL-M-38510/20302 BEB | QPL I  |

| HM1-7620     | MIL-M-38510/20401 BEB | QPL I  |

| HM1-7621     | MIL-M-38510/20402 BEB | QPL I  |

| HM1-7642     | MIL-M-38510/20601 BVB | QPL II |

| HM1-7643     | MIL-M-38510/20602 BVB | QPL II |

| HM1-7644     | MIL-M-38510/20603 BEB | QPL II |

| HM1-7602     | MIL-M-38510/20701 BEB | QPL II |

| HM1-7603     | MIL-M-38510/20702 BEB | QPL II |

| HM1-7640     | MIL-M-38510/20801 BJB | QPL II |

| HM1-7641     | MIL-M-38510/20802 BJB | QPL II |

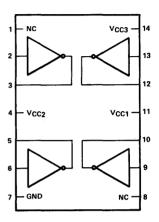

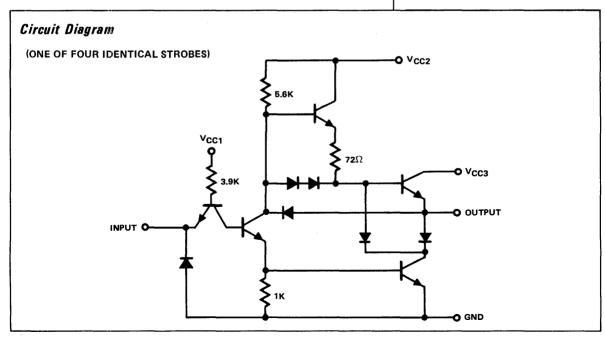

# HD-6600 QUAD POWER STROBE

FEBRUARY 1978

#### Features

- HIGH DRIVE CURRENT—200mA

- HIGH SPEED 50ns TYPICAL

- TTL COMPATIBLE INPUTS

- DIELECTRIC ISOLATION

- QUAD MONOLITHIC CONSTRUCTION

- POWER SUPPLY FLEXIBILITY

- LOW POWER:

STANDBY-30mW/CIRCUIT ACTIVE-95mW/CIRCUIT

#### Description

The HD-6600 Quad Power Strobe is constructed with Harris Dielectric Isolation Bipolar Monolithic Process. The design incorporates power supply flexibility with TTL compatible inputs and high current outputs. This circuit is intended for use in power switched PROM arrays.

#### Logic Diagram

2

#### Specifications HD-6600

#### **ABSOLUTE MAXIMUM RATINGS**

Power Supply Voltage VCC1 VCC2

22 +18 VDC 23 +18 VDC

VCC3

Input Voltage V<sub>IN</sub>

Storage Temperature T<sub>STG</sub>

Output Current I<sub>L</sub>

-0.5 VDC to +5.5 VDC -65°C to +150°C -200mA

+8 VDC

Power Dissipation at 25°C

1000mW (Derate 9mW/°C Above 60°C)

#### RECOMMENDED OPERATING CONDITIONS

Power Supplies:

5 VDC ± 10%

VCC1 VCC2 VCC3

12 VDC ± 15% 5 VDC ± 20%

ELECTRICAL CHARACTERISTICS

$T_A = -55$ °C to +125°C HD1-6600-2

VCC2 = 12.0 VDC

TA = 0°C to +75°C HD1-6600-5

VCC3 = 5.0 VDC

| SYMBOL           | PARAMETER                  | MIN. | TYP. | MAX.       | UNITS    | TEST CO                                                 | ONDITIONS                  |

|------------------|----------------------------|------|------|------------|----------|---------------------------------------------------------|----------------------------|

| I <sub>IR</sub>  | Input Current              |      |      | 60<br>-1.6 | μA<br>mA | V <sub>IN</sub> = 2.4 VDC<br>V <sub>IN</sub> = 0.4 VDC  | V <sub>CC1</sub> = 5.5 VDC |

| VIH<br>VIL       | Input Threshold<br>Voltage | 2.0  |      | 0.8        | V<br>V   | V <sub>CC1</sub> = 4.5 VDC                              |                            |

| Voн              | Output Voltage             | 4.75 | 4.85 |            | ٧        | V <sub>CC1</sub> = 5.0 VDC<br>V <sub>IN</sub> = 0.4 VDC | I <sub>L</sub> = -150mA DC |

| VOL              | (Note 1)                   |      |      | 1.0        | V        | V <sub>CC1</sub> = 5.0 VDC                              | IL = 500 μA DC             |

| I <sub>CC1</sub> |                            |      | 4    | 6.0        | mA       | V <sub>CC1</sub> = 5.5 VDC                              | V <sub>IN</sub> = 2.4 VDC  |

| I <sub>CC2</sub> | Supply Current             |      | 40   | 70         | mA       | V <sub>CC1</sub> = 5.5 VDC<br>V <sub>IN</sub> = 0.4 VDC | IL = -150mA DC             |

| I <sub>CC2</sub> | (Note 2)                   |      | 8    | 15         | mA       | V <sub>CC1</sub> = 5.5 VDC<br>V <sub>IN</sub> = 2.4 VDC | I <sub>L</sub> = 0         |

A.C.

D.C.

|   | SYMBOL | PARAMETER      | TYP. | MAX. | UNITS | CONDITIONS TA = 25°C |

|---|--------|----------------|------|------|-------|----------------------|

|   | tON    | Turn On Delay  | 50   | 75   | ns    | VCC1 = 5.0 VDC       |

|   | tOFF   | Turn Off Delay | 50   | 75   | ns    | VCC2 = 12 VDC        |

| 4 |        |                |      | 1    |       | VCC3 = 5.0 VDC       |

|   | tR     | Rise Time      | 40   | 65   | ns    | R <sub>L</sub> = 33Ω |

|   | tF     | Fall Time      | 40   | 65   | ns    | CL = 620 pF          |

NOTES (1) One strobe enabled. (2) All strobes enabled.

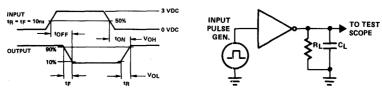

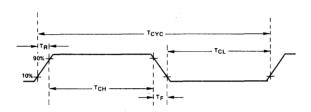

#### **Switching Time Definitions**

#### Typical Characteristics

# MONOLITHIC DIODE MATRICES

#### Features

- FIELD PROGRAMMABLE

- CMOS COMPATIBLE

- ZERO POWER DISSIPATION

- FAST SWITCHING

- FIVE POPULAR ORGANIZATIONS

#### Description

Designed with the CMOS circuit engineer in mind, these versatile diode matrices allow the application of logically powerful programmable solutions to low power CMOS system applications.

These devices incorporate an advanced dielectric isolation process to eliminate the need for power supply pins and allow parasitic free operation.

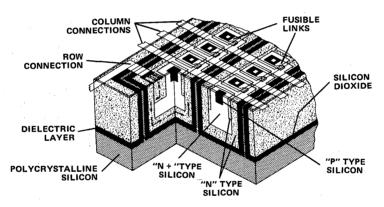

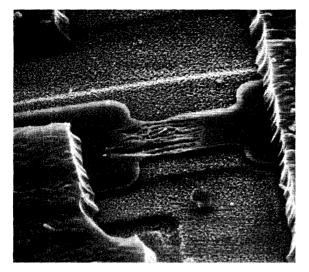

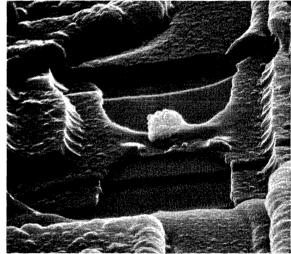

Programming is accomplished by cleanly vaporizing a fusible link by application of a brief high voltage pulse to a selected array element. This operation open circuits a row to column orring diode eliminating their former interaction.

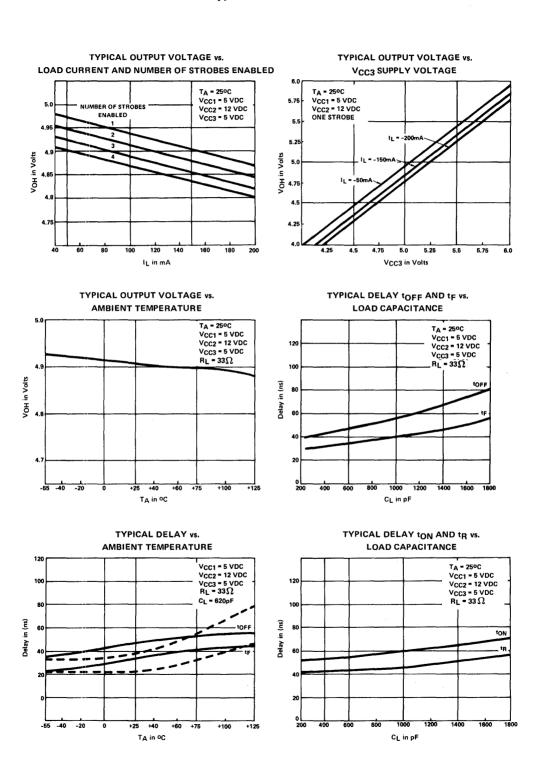

#### Monolithic Structure

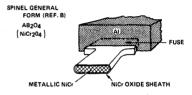

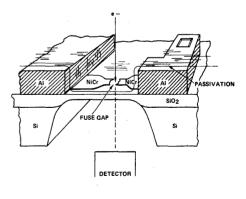

#### Fusible Link System

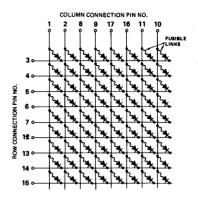

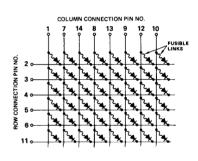

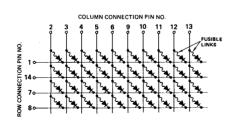

#### Monolithic Diode Matrices

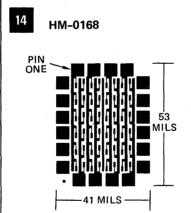

#### HM-0168 6 x 8 DIODE MATRICES

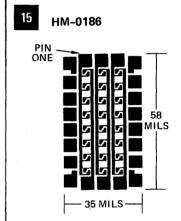

HM-0186 8 x 6 DIODE MATRICES

HM-0410 4 x 10 DIODE MATRICES

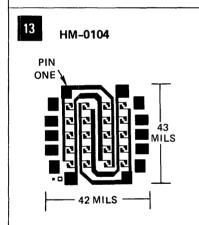

HM-0104 10 x 4 DIODE MATRICES

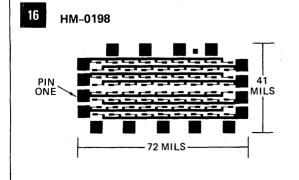

HM-0198 9 x 8 DIODE MATRICES

#### HM-0104

#### HM-0168

#### HM-0410

#### HM-0186

#### **CUSTOM PATTERNS**

When ordering a matrix with a custom pattern: Send a paper tape, or copy a matrix pattern and circle out those diodes to be removed from the matrix. Another method to clearly identify a pattern is to call out respective anode and cathode for each diode to be removed, by package pin number.

#### Specifications Diode Matrices

#### **ABSOLUTE MAXIMUM RATINGS**

Forward Current

100mA

Surge Current (100 µs Max.)

200mA

Total Ckt. Dissipation (Still Air)

450mW

Storage Temperature (Ambient)

-65°C to +150°C

Maximum Ratings are limiting values above which permanent damage may occur.

HM-0XXX-2

#### **ELECTRICAL CHARACTERISTICS**

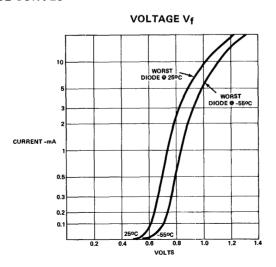

|                 |                            | HM-0   | XXX-5      | HM-0    | 8-XXX     | ŀ     |                                                                   |

|-----------------|----------------------------|--------|------------|---------|-----------|-------|-------------------------------------------------------------------|

|                 | TA                         | 0°C to | + 75°C     | -55°C t | o +125°C  |       |                                                                   |

| SYMBOL          | PARAMETER                  | MIN    | MAX        | MIN     | MAX       | UNITS | CONDITIONS                                                        |

| ٧F              | Forward Voltage            |        | 1.5<br>0.9 |         | 1.5<br>.9 | v     | I <sub>F</sub> = 20mA<br>I <sub>F</sub> = 1mA                     |

| B∨R             | Reverse Breakdown Voltage  | 20     |            | 30      |           | v     | Ι <sub>ΒV</sub> = 100μΑ                                           |

| <u>}</u>        |                            | 25     | ec.        | 2!      | 5°C       |       |                                                                   |

| t <sub>rr</sub> | Reverse Recovery Time      |        | 100        |         | 50        | ns    | I <sub>F</sub> = 10mA to I <sub>R</sub> = 10mA<br>Recovery to 1mA |

| cc              | Crosspoint Capacitance (1) |        |            |         | 8         | pF    | V <sub>R</sub> = 5V; f = 1MHz (2)                                 |

| 1               |                            | 1      | 1          | l       |           | l     | 1                                                                 |

(1) Guaranteed but not 100% tested.

(2) CC  $\propto \frac{1}{\text{VBIAS}}$

#### **TYPICAL PERFORMANCE CURVES**

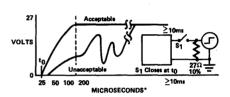

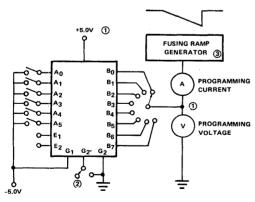

#### **Programming**

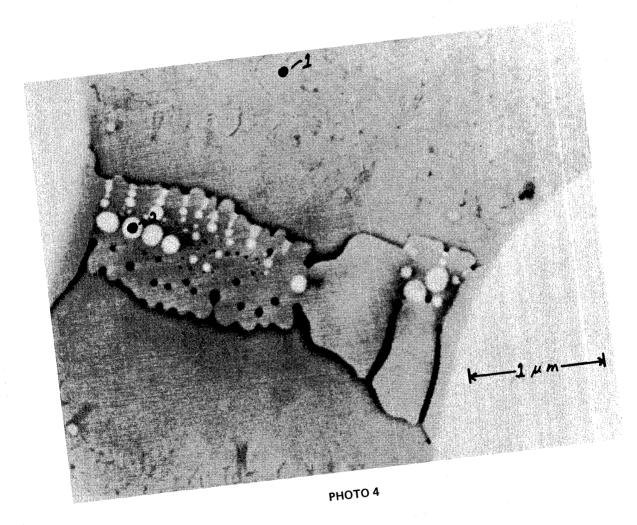

Use a simple supply capable of driving a 27 ohm resistor (carbon) with a clean transition from 0 to 24-30 volts in less than  $500\,\mu s$ , for at least 10ms. The diode to be disconnected is selected by setting the row and column switches S2 and S3 respectively as required. When switch S1 is depressed, programming current is provided to column contacts in the matrix. This current opens the fusible link, in series with the selected diode. The peak fusing current required to open a fusible link is approximately 750 milliamperes. As the temperature of the fuse is raised, the aluminum begins to melt. This melting continues until the fuse link separates. The cohesive forces of the melting aluminum retracts the remaining portions of the metal, thereby preventing formation of loose aluminum residues. The melting temperature of aluminum (approximately 650°C) will not affect the passivating layer of silicon dioxide, whose melting temperature is about 1350°C. Test verification is obtained by an indicator lamp or LED placed in series with the column and row switches through the verify contacts of S1 to give electrical indication of the condition of each diode in the matrix before and after fusing.

Caution: Programming is limited to one fuse at a time.

#### SIMPLE PROGRAMMER

# \*24 TO 30 VOLTS 1 AMP MINIMUM S1 DPDT MOMENTARY S2 17 POS, 1 POLE S3 ROTARY Q1 Q2 - 2N1613 INDICATOR LIGHT, LED S2 TO FUSE S1B COLUMN S3 MATRIX UNDER TEST

#### PROGRAMMER TEST CONFIGURATION

\*Max TRISE = 500 µ sec

NOTE: The 27 ohm resistor is only used for oscilloscope measurements of the Power Supply Characteristics becaues it represents a typical unprogrammed fuse/diode.

# HM-7602/03

32 x 8 PROM

HM-7602 — Open Collector Outputs HM-7603 — "Three State" Outputs

#### Features

- 50ns MAXIMUM ADDRESS ACCESS TIME

- "THREE STATE" OR OPEN COLLECTOR OUTPUTS

- SIMPLE HIGH SPEED PROGRAMMING PROCEDURE ONE PULSE/BIT. ASSURES FAST PROGRAMMING AND SUPERIOR RELIABILITY.

- FAST ACCESS TIME GUARANTEED FOR WORST CASE N<sup>2</sup> SEQUENC-ING OVER COMMERCIAL AND MILITARY TEMPERATURE AND VOLT-AGE RANGES.

- INDUSTRY'S HIGHEST PROGRAMMING YIELD

#### Description

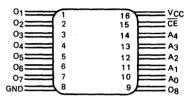

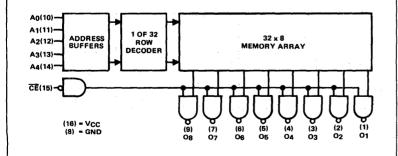

The HM-7602/03 is a fully decoded high speed Schottky TTL 256/Bit Field Programmable ROM in a 32 word by 8 bit/word format with open collector (HM-7602) or "Three State" (HM-7603) outputs. These PROMs are available in a 16 pin D.I.P. (ceramic or epoxy) and a 16 pin flatpack.

All bits are manufactured storing a logical "1" (Positive Logic) and can be selectively programmed for a logical "0" in any one bit position.

Nickel-chromium fuse technology is used on this and all other Harris Bipolar PROMs.

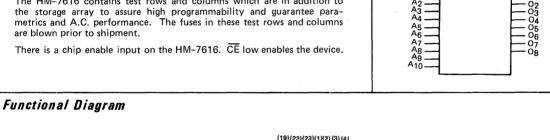

The HM-7602/03 contains test rows which are in addition to the storage array to assure high programmability and guarantee parametric and A.C. performance. The fuses in these test rows are blown prior to shipment.

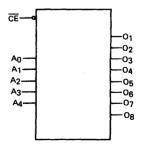

There is one chip enable input on the HM-7602/03.  $\overline{\text{CE}}$  low enables the chip.

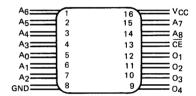

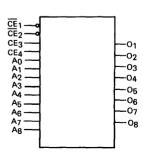

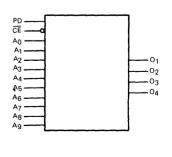

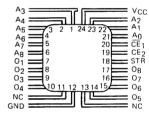

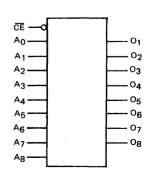

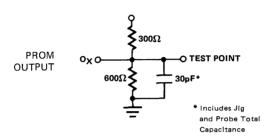

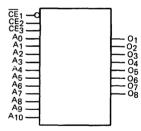

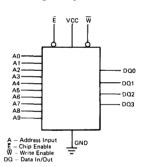

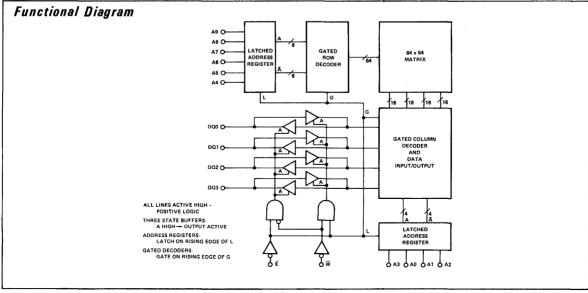

#### Pinouts

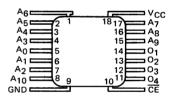

TOP VIEW - DIP

TOP VIEW - FLATPACK

PIN NAMES

A0 - A4 Address Inputs

O1 - O8 Data Outputs

CE Chip Enable Inputs

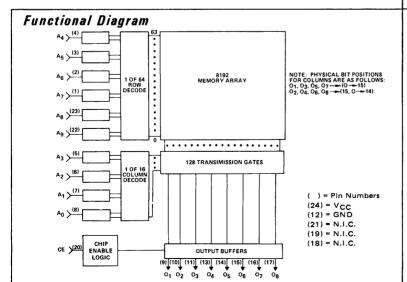

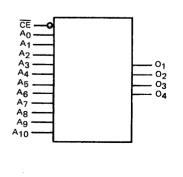

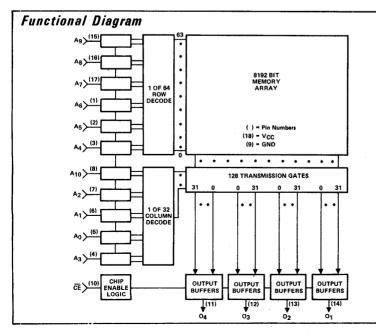

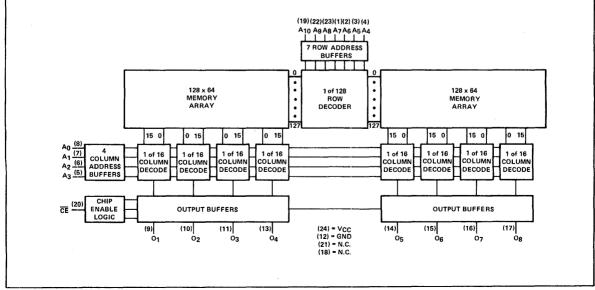

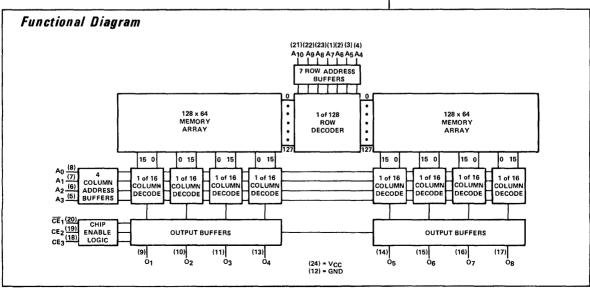

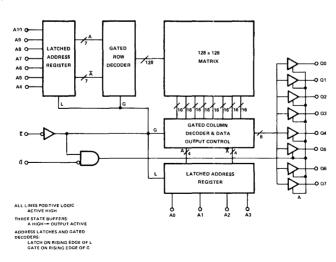

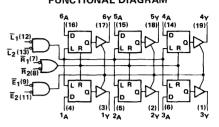

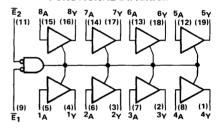

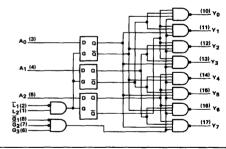

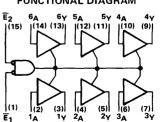

#### Functional Diagram

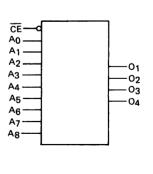

#### Logic Symbol

#### Specifications HM-7602/03

#### **ABSOLUTE MAXIMUM RATINGS**

Output or Supply Voltage (Operating) -0.3 to +7.0V Storage Temperature -65°C to +150°C Address/Enable Input Voltage 5.5V Operating Temperature (Ambient) -55°C to +125°C Address/Enable Input Current -20mA Maximum Junction Temperature +175°C

Output Sink Current 100mA

CAUTION: Stresses above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and functional operation of the device at these or at any other conditions above those indicated in the operational sections of this specification is not implied. (While programming, follow the programming specifications.)

#### D.C. ELECTRICAL CHARACTERISTICS (Operating)

HM-7602/03-5 (V $_{\rm CC}$  = 5.0V  $^\pm$ 5%, T $_{\rm A}$  = 0°C to +75°C) HM-7602/03-2 (V $_{\rm CC}$  = 5.0V  $^\pm$ 10%, T $_{\rm A}$  = -55°C to +125°C) Typical measurements are at T $_{\rm A}$  = 25°C, V $_{\rm CC}$  = +5V

| SYMBOL     | PARAMETER                               | MIN  | TYP          | MAX          | UNITS            | TEST CONDITIONS                                                           |

|------------|-----------------------------------------|------|--------------|--------------|------------------|---------------------------------------------------------------------------|

| HH<br>HL   | Address/Enable "1"<br>Input Current "0" | _    | _<br>-50.0   | +40<br>-250  | μΑ<br>μΑ         | VIH = VCC Max.<br>VIL = 0.45V                                             |

| VIH        | Input Threshold "1"<br>Voltage "0"      | 2.0  | 1.5<br>1.5   | _<br>0.8     | V                | VCC = VCC Min<br>VCC = VCC Max.                                           |

| VOH<br>VOL | Output Voltage "1" "0"                  | 2.4* | 3.2*<br>0.35 | _<br>0.45    | V                | IOH = -2.0mA, VCC = VCC Min.<br>IOL = +16mA, VCC = VCC Min.               |

| IOLE       | Output Disable "1"<br>Current "0"       | _    | =            | +100<br>-100 | μ <u>Α</u><br>μΑ | VOH, VCC = VCC Max.<br>VOL = 0.3V, VCC = VCC Max.                         |

| VCL        | Input Clamp Voltage                     | _    | -            | -1.2         | V                | IIN = -18mA                                                               |

| IOS        | Output Short Circuit<br>Current         | -15* | _            | -100*        | mA               | VCC = VCC Max., VOUT = 0.0V<br>One Output Only for a Max.<br>of 1 Second. |

| Icc        | Power Supply Current                    | _    | 90           | 130          | mA               | VCC = VCC Max. All Inputs<br>Grounded                                     |

NOTE: Positive current defined as into device terminals

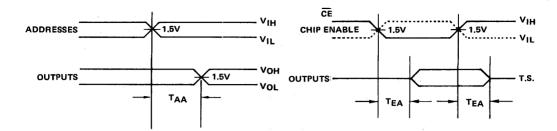

#### A.C. ELECTRICAL CHARACTERISTICS (Operating)

|            |                                                |     | HM-7602/03-5<br>5V ±5%<br>0°C to +75°C |          |     | HM-7602/03-2<br>5V ±10%<br>-55°C to +125°C |          |          |  |

|------------|------------------------------------------------|-----|----------------------------------------|----------|-----|--------------------------------------------|----------|----------|--|

| SYMBOL     | PARAMETER                                      | MIN | TYP                                    | MAX*     | MIN | TYP                                        | MAX*     | UNITS    |  |

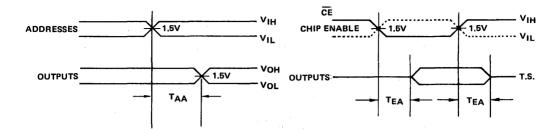

| TAA<br>TEA | Address Access Time<br>Chip Enable Access Time | -   | 30<br>20                               | 50<br>35 | _   | -<br>-                                     | 60<br>50 | ns<br>ns |  |

<sup>\*</sup>A.C. limits guaranteed for worst case N2 sequencing with maximum test frequency of 5MHz.

#### CAPACITANCE: TA = 25°C

| SYMBOL      | PARAMETER          | MAXIMUM | UNITS | TEST CONDITIONS                 |

|-------------|--------------------|---------|-------|---------------------------------|

| CINA, CINCE | Input Capacitance  | 12      | pF    | VCC = 5V, VIN = 2.0V, f = 1MHz  |

| COUT        | Output Capacitance | 12      | pF    | VCC = 5V, VOUT = 2.0V, f = 1MHz |

<sup>\* &</sup>quot;Three State" only

#### 2

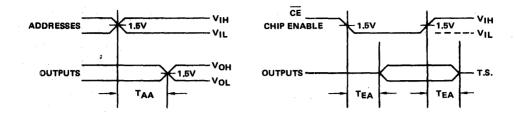

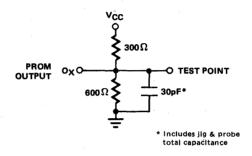

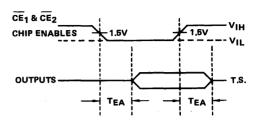

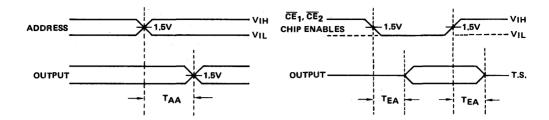

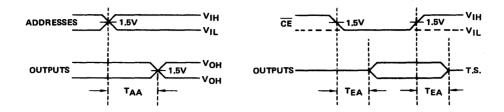

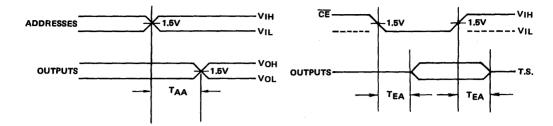

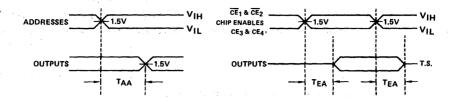

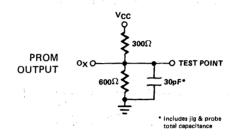

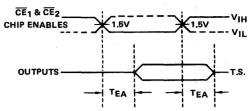

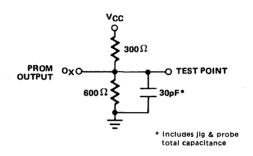

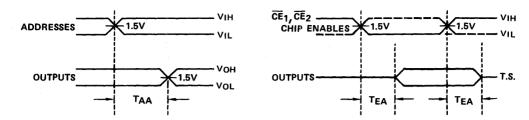

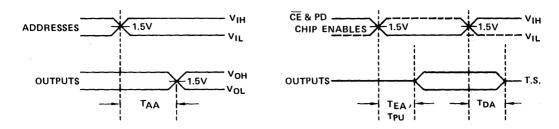

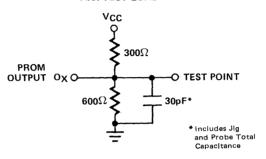

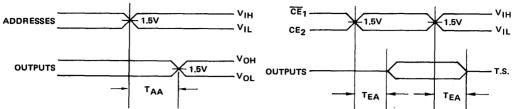

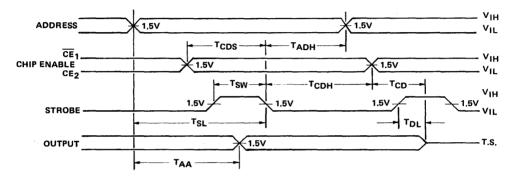

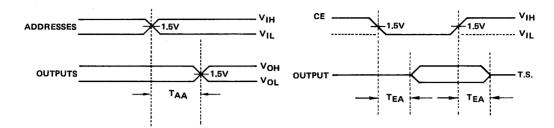

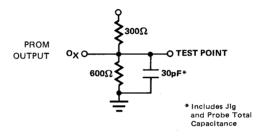

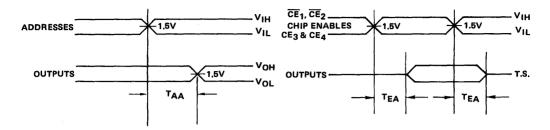

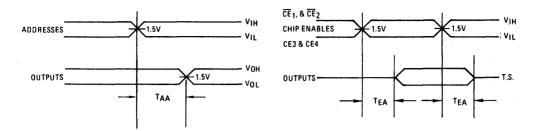

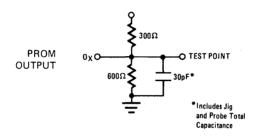

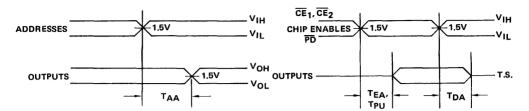

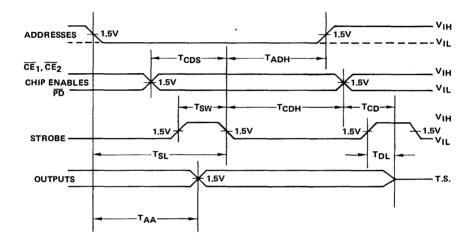

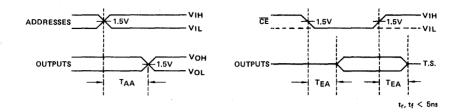

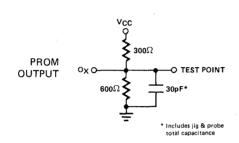

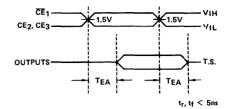

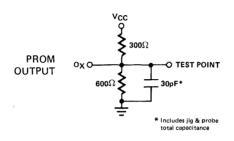

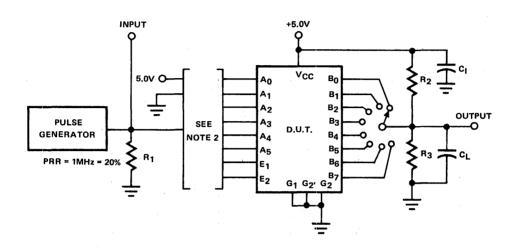

#### **SWITCHING TIME DEFINITIONS**

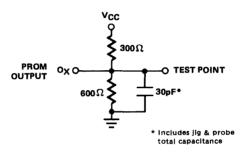

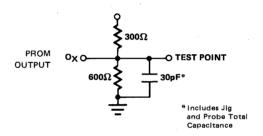

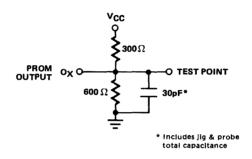

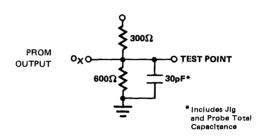

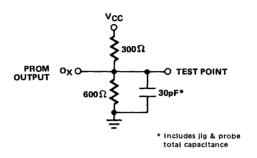

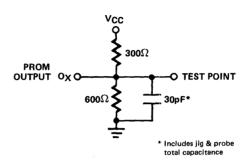

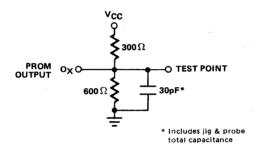

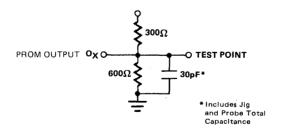

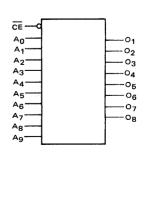

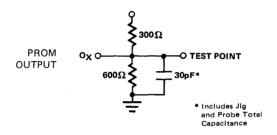

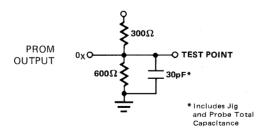

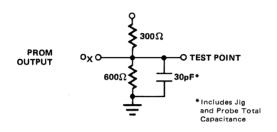

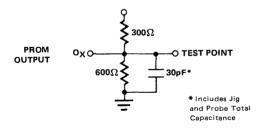

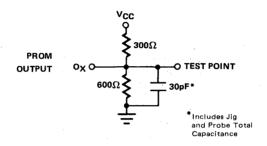

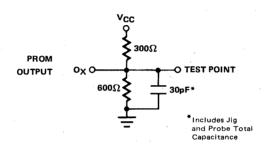

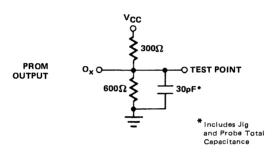

A. C. TEST LOAD

## HM-7610/11

256 x 4 PROM

HM-7610 — Open Collector Outputs HM-7611 — "Three State" Outputs

#### Features

- 60ns MAXIMUM ADDRESS ACCESS TIME

- "THREE STATE" OR OPEN COLLECTOR OUTPUTS

- SIMPLE, HIGH SPEED PROGRAMMING PROCEDURE USING SINGLE PULSES, ASSURES FAST PROGRAMMING AND SUPERIOR RELIABILITY

- INPUTS AND OUTPUT TTL COMPATIBLE

- FAST ACCESS TIME GUARANTEED FOR WORST CASE N<sup>2</sup> SEQUENCING OVER COMMERCIAL AND MILITARY TEMPERATURE AND VOLTAGE RANGES.

- INDUSTRY'S HIGHEST PROGRAMMING YIELD

- PIN COMPATIBLE WITH INDUSTRY STANDARD PROMs AND ROMs

#### Description

The HM-7610/11 are fully decoded high speed Schottky TTL 1024-Bit Field Programmable ROMs in a 256 word by 4 bit/word format with open collector (HM-7610) or "three state" (HM-7611) outputs. These PROMs are available in 16 pin D.I.P. (ceramic or epoxy) and a 16 pin flatpack.

All bits are manufactured storing a logical "1" (positive logic) and can be selectively programmed for a logical "0" in any bit position.

The HM-7610/11 contain test rows and columns which are in addition to the storage array to assure high programmability and guarantee parametric and A.C. performance. The fuses in these test rows and columns are blown prior to shipment.

Nickel-chromium fuse technology is used on this and all other Harris Bipolar PROMs.

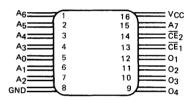

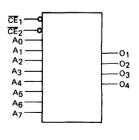

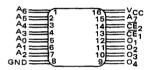

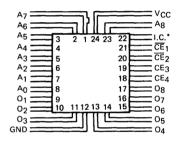

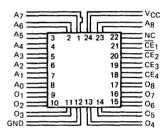

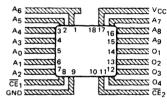

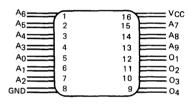

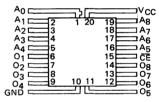

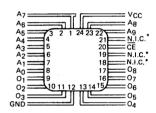

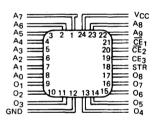

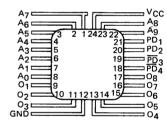

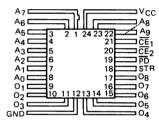

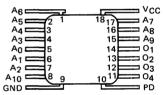

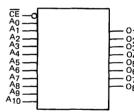

#### **Pinouts**

TOP VIEW-DIP

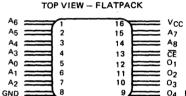

TOP VIEW-FLATPACK

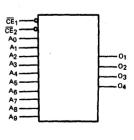

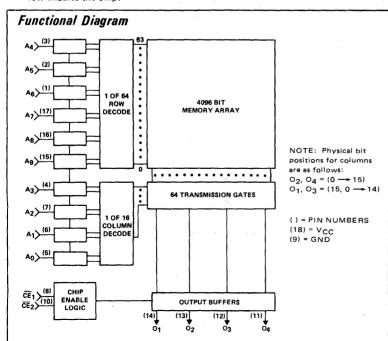

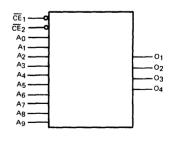

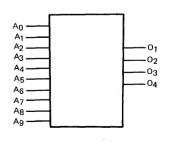

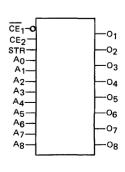

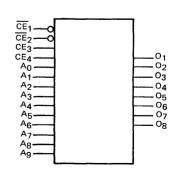

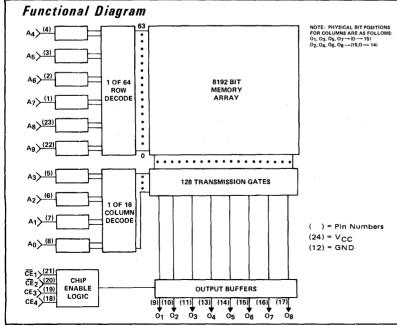

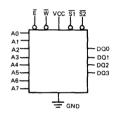

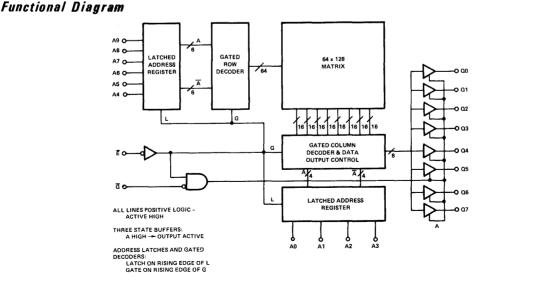

#### PIN NAMES

$\begin{array}{ccc} \underline{A_0} - \underline{A_7} & \text{Address Inputs} \\ \overline{CE_1} - \overline{CE_2} & \text{Chip Enable Inputs} \\ O_1 - O_4 & \text{Data Outputs} \end{array}$

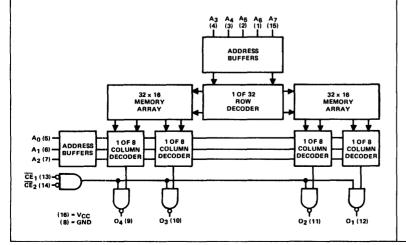

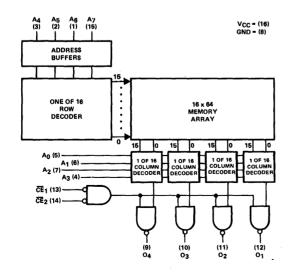

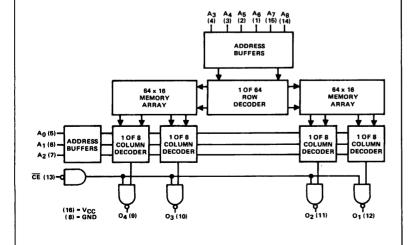

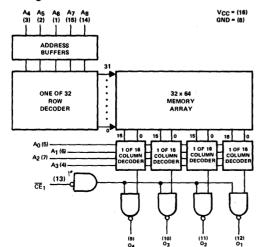

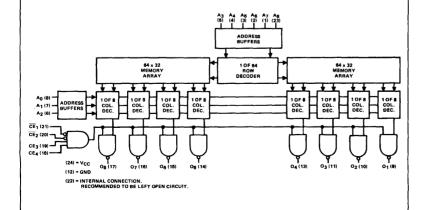

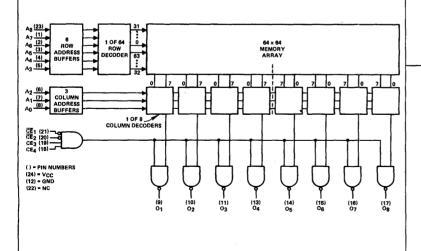

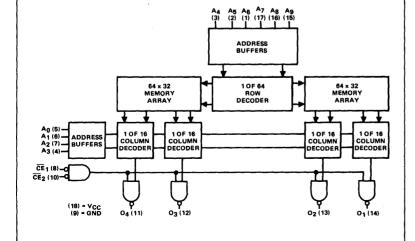

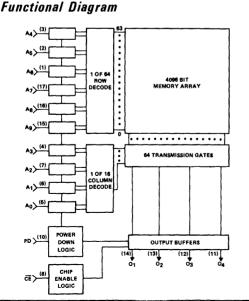

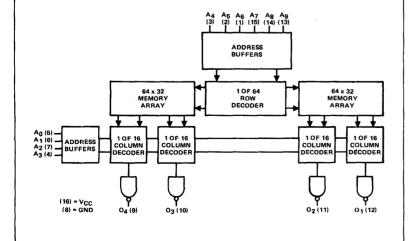

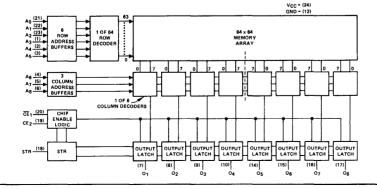

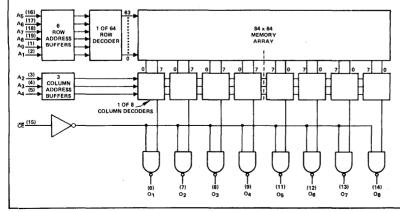

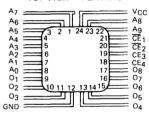

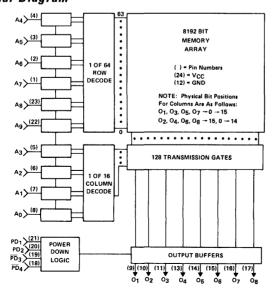

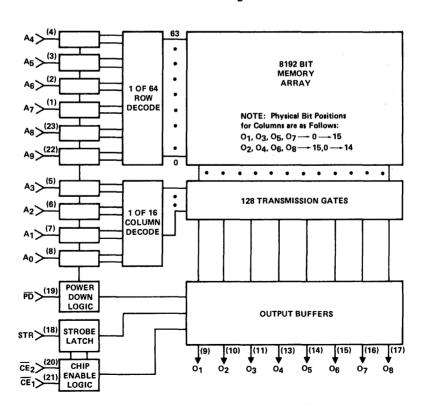

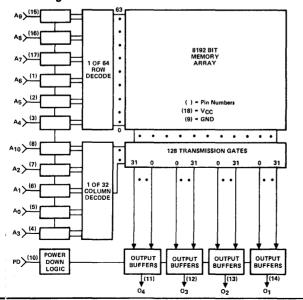

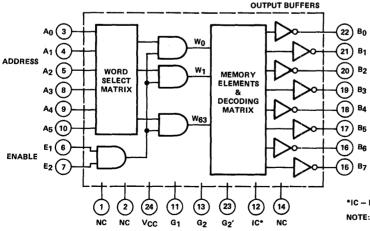

#### Functional Diagram

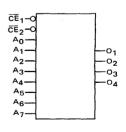

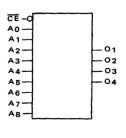

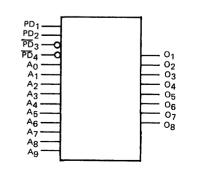

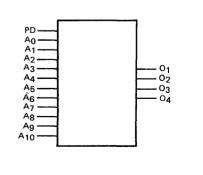

#### Logic Symbol

#### Specifications HM-7610/11

#### **ABSOLUTE MAXIMUM RATINGS**

Output or Supply Voltage (Operating) -0.3 to +7.0V Storage Temperature -65°C to +150°C Address/Enable Input Voltage 5.5V Operating Temperature (Ambient) -55°C to +125°C Address/Enable Input Current -20mA Maximum Junction Temperature +175°C Output Sink Current 100mA

CAUTION: Stresses above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and functional operation of the device at these or at any other conditions above those indicated in the operational sections of this specification is not implied. (While programming, follow the programming specifications.)

#### D.C. ELECTRICAL CHARACTERISTICS (Operating)

HM-7610/11-5 (V $_{\rm CC}$  = 5.0V ±5%, T $_{\rm A}$  - 0°C to +75°C) HM-7610/11-2 (V $_{\rm CC}$  = 5.0V ±10%, T $_{\rm A}$  = -55°C to +125°C) Typical measurements are at T $_{\rm A}$  = 25°C, V $_{\rm CC}$  = +5V

| SYMBOL     | PARAMETER                               | MIN .     | TYP          | MAX          | UNITS    | TEST CONDITIONS                                                           |

|------------|-----------------------------------------|-----------|--------------|--------------|----------|---------------------------------------------------------------------------|

| HH<br>HL   | Address/Enable "1"<br>Input Current "0" | _         | _<br>-50.0   | +40<br>-250  | μΑ<br>μΑ | VIH = VCC Max.<br>VIL = 0.45V                                             |

| ViH<br>VIL | Input Threshold "1"<br>Voltage "0"      | 2.0<br>-  | 1.5<br>1.5   | 0.8          | V        | VCC = VCC Min<br>VCC = VCC Max.                                           |

| Voh<br>Vol | Output Voltage "1" "0"                  | 2.4*<br>_ | 3.2*<br>0.35 | _<br>0.45    | V        | IOH = -2.0mA, VCC = VCC Min.<br>IOL = +16mA, VCC = VCC Min.               |

| IOHE       | Output Disable "1"<br>Current "0"       | _         | _            | +100<br>-100 | μΑ<br>μΑ | VOH, VCC = VCC Max.<br>VOL = 0.3V, VCC = VCC Max.                         |

| VCL        | Input Clamp Voltage                     | _         | -            | -1,2         | V        | IIN = -18mA                                                               |

| Ios        | Output Short Circuit<br>Current         | -15*      | -            | -100*        | mA       | VCC = VCC Max., VOUT = 0.0V<br>One Output Only for a Max.<br>of 1 Second. |

| ICC        | Power Supply Current                    | _         | 90           | 130          | mA       | VCC = VCC Max. All Inputs<br>Grounded                                     |

NOTE: Positive current defined as into device terminals

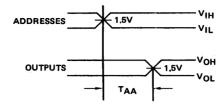

#### A.C. ELECTRICAL CHARACTERISTICS (Operating)

|        |                         |     | HM-7610/11-5<br>5V ±5%<br>0°C to +75°C |      | H<br>-5! |     |      |       |

|--------|-------------------------|-----|----------------------------------------|------|----------|-----|------|-------|

| SYMBOL | PARAMETER               | MIN | TYP                                    | MAX* | MIN      | TYP | MAX* | UNITS |

| TAA    | Address Access Time     |     | 40                                     | 60   | _        | _   | 75   | ns    |

| TEA    | Chip Enable Access Time | -   | 15                                     | 25   | -        | -   | 30   | ns    |

<sup>\*</sup>A.C. limits guaranteed for worst case N2 sequencing with maximum test frequency of 5MHz.

#### CAPACITANCE: TA = 25°C

| SYMBOL      | PARAMETER          | MAXIMUM | UNITS | TEST CONDITIONS                 |

|-------------|--------------------|---------|-------|---------------------------------|

| CINA, CINCE | Input Capacitance  | 12      | pF    | VCC = 5V, VIN = 2.0V, f = 1MHz  |

| COUT        | Output Capacitance | 12      | pF    | VCC = 5V, VOUT = 2.0V, f = 1MHz |

<sup>\*</sup>Not applicable to open collector.

#### A. C. TEST LOAD

2

## HM-7610A/11A

#### HIGH SPEED 256 x 4 PROM

HM-7610A - Open Collector Outputs HM-7611A - "Three State" Outputs

#### Features

- 45ns MAXIMUM ADDRESS ACCESS TIME

- "THREE STATE" OR OPEN COLLECTOR OUTPUTS

- SIMPLE, HIGH SPEED PROGRAMMING PROCEDURE USING SINGLE PULSES, ASSURES FAST PROGRAMMING AND SUPERIOR RELIABILITY

- INPUTS AND OUTPUTS TTL COMPATIBLE

- FAST ACCESS TIME GUARANTEED FOR WORST CAST N<sup>2</sup> SEQUENCING OVER COMMERCIAL AND MILITARY TEMPERATURE AND VOLTAGE RANGES.

- INDUSTRY'S HIGHEST PROGRAMMING YIELD

- PIN COMPATIBLE WITH INDUSTRY STANDARD PROM's AND ROM's

#### Description

The HM-7610A/11A are fully decoded high speed Schottky TTL 1024-Bit Field Programmable ROMs in a 256 word by 4 bit/word format with open collector (HM-7610A) or "three state" (HM-7611A) outputs. These PROMs are available in 16 pin D.I.P. (ceramic or epoxy) and a 16 pin flatpack.

All bits are manufactured storing a logical "1" (positive logic) and can be selectively programmed for a logical "0" in any bit position.

The HM-7610A/11A contain test rows and columns which are in addition to the storage array to assure high programmability and guarantee parametric and A.C. performance. The fuses in these test rows and columns are blown prior to shipment.

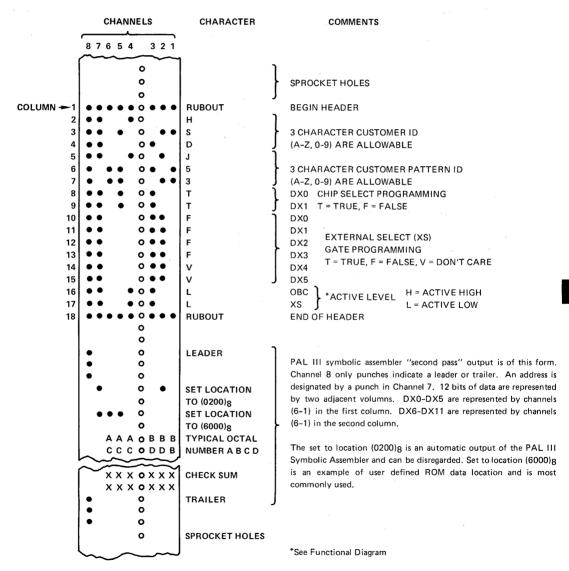

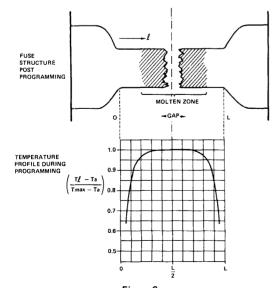

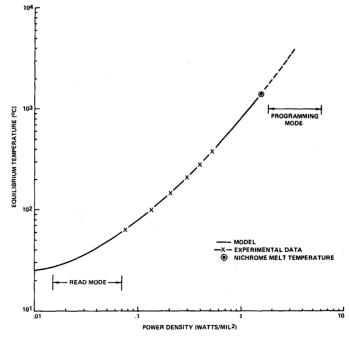

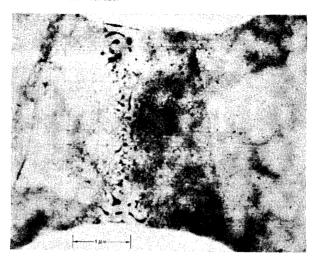

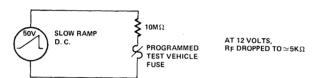

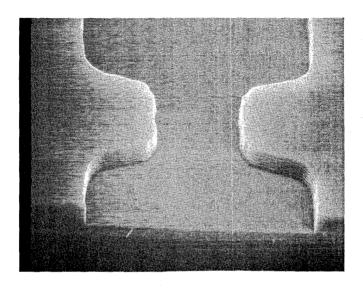

This PROM is intended for use in state of the art high speed logic systems.